## ASSP

# FeRAM Embedded UHF Band RFID LSI

## **For Battery-less Solution**

## MB97R8110

## ■ 1. OVERVIEW

This document provides LSI specifications for the passive RFID Tag LSI "MB97R8110" (USER bank 8kBytes) based on "EPCglobal Class 1 Generation 2 Ver.1.2.0".

In this specification, the term "interrogator" used in EPCglobal standard is described as R/W (reader/writer). The term "Tag" is used as is.

## 1.1 FEATURES

• Compliant with EPCglobal Class 1 Generation 2 (C1G2)

-Carrier frequency: 860 to 960 MHz

- -Data rate

- $R/W \rightarrow Tag: 26.7$  kbps to 128 kbps (assuming equiprobable data)

- Tag  $\rightarrow$  R/W: 40 kbps to 640 kbps

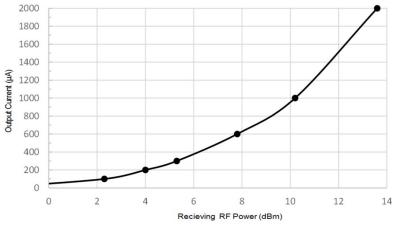

- RF Generated Power supply to external devices (3.0V 600uA output from +8dBm RF input)

- Serial Interface (SPI)

- -Slave mode operation : USER memory area can be read/written through SPI.

- -Master mode operation : External SPI slave device can be controlled through SPI.

- -Arbitration feature between RF and SPI access controlled by SPIREQ and SPIACK.

- Key Matrix Scan Interface

- FeRAM: Non-volatile memory with High speed read and write

- -USER bank size: 61,440 bits\*

- -EPC length: up to 480bits

- -BlockPermalock: 8 Areas of USER bank to be write-protected in units of 512 words (=8,192bits).

- -Read/Write Endurance: 10<sup>13</sup> times.

- -Memory data retention: 10 years (+85 °C)

\*In SPI Master communication, 28,672bits of memory can be allocated for the buffer of data to be transferred to external slave device and the storage of response data from external SPI slave device.

Fujitsu Semiconductor Memory Solutions Limited has changed its name to RAMXEED Limited. RAMXEED Limited will continue to offer and support existing products while maintaining Fujitsu's part number unchanged.

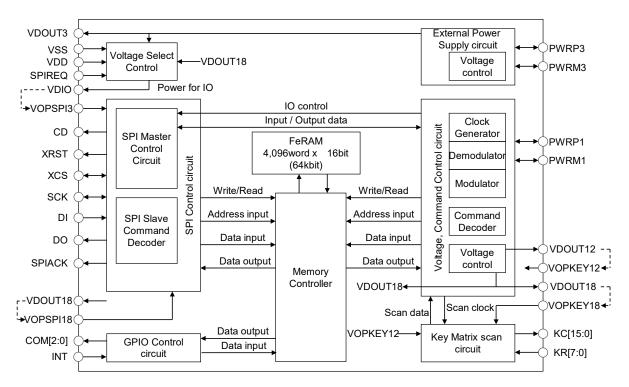

## ■ 1.2 BLOCK DIAGRAM

Figure 1.2 - BLOCK DIAGRAM

## ■ 1.3 PAD CONFIGURATION

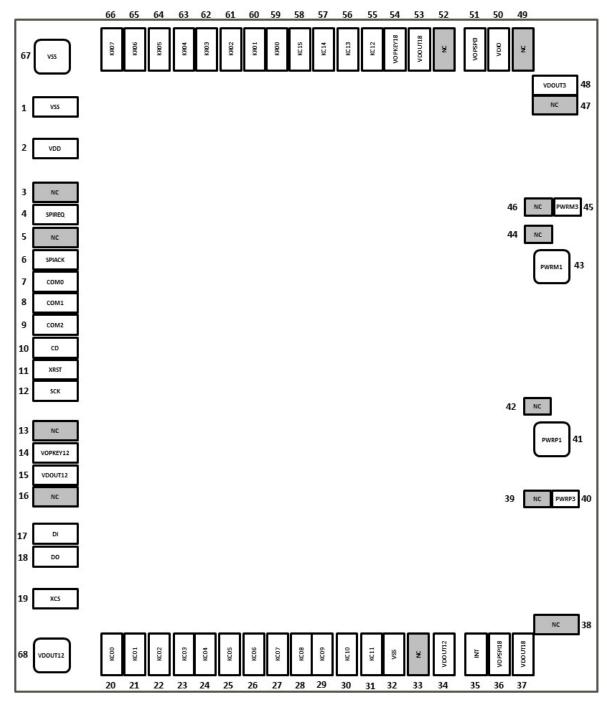

#### ■ 1.3.1 Pad Layout

Figure 1.3.1 shows PAD Layout.

Figure 1.3.1 Pad Layout

## ■ 1.3.2 Pad Information

Table 1.3.2.1 shows PAD configuration and Power source. Table 1.3.2.2, 1.3.2.3 and Table 1.3.2.4 show Pad status of SPI, GPIO and Key Matrix scan respectively depending on the condition. Table 1.3.2.1 Pad configuration and Power source

|    | Pad Name        | In / Out          | Power Source  | Terminal            | Function Description                                            |

|----|-----------------|-------------------|---------------|---------------------|-----------------------------------------------------------------|

|    | VSS             | VSS               | -             | -                   | Ground                                                          |

|    | VDD             | In (Power)        | -             | -                   | External power input for SPI Slave communication (3V)           |

|    | NC              | -                 | -             | -                   | Open                                                            |

| 4  | SPIREQ          | In                | VOPSPI3       | Pull Down(1MΩ)      | SPI Slave request input                                         |

| 5  | NC              | -                 | -             | -                   | Open                                                            |

|    | SPIACK          | Out               | VOPSPI3       | -                   | Response to SPI Slave request (SPI Status output)               |

|    | COM0            | Out               | VOPSPI3       | -                   | GPIO (register data output)                                     |

| 8  | COM1            | Out               | VOPSPI3       | -                   | GPIO (register data output)                                     |

| 9  | COM2            | Out               | VOPSPI3       | -                   | GPIO (register data output)                                     |

| 10 | CD              | Out               | VOPSPI3       | -                   | Command/Data output                                             |

| 11 | XRST            | Out               | VOPSPI3       | -                   | Reset output                                                    |

| 12 | SCK             | In/Out            | VOPSPI3       | -                   | SPI Clock                                                       |

|    | NC              | -                 | -             | -                   | Open                                                            |

| 14 | VOPKEY12        | In (Power)        | -             | Pull Down(6MΩ)      | Power input for Key Matrix scan circuit (connect to pad15)      |

| 15 | VDOUT12         | Out (Power)       | -             | -                   | Internally generated power output (1.2V)                        |

| 16 | NC              | -                 | -             | -                   | Open                                                            |

| 17 | DI              | In                | VOPSPI3       | -                   | SPI Data input                                                  |

|    | DO              | Out               | VOPSPI3       | -                   | SPI Data output                                                 |

|    | XCS             | In/Out            | VOPSPI3       | -                   | SPI Chip select                                                 |

|    | KC00            | Out               | VOPKEY18      | -                   | Key Matrix scan pulse output                                    |

|    | KC01            | Out               | VOPKEY18      |                     | Key Matrix scan pulse output                                    |

|    | KC02            | Out               | VOPKEY18      | -                   | Key Matrix scan pulse output                                    |

|    | KC03            | Out               | VOPKEY18      | -                   | Key Matrix scan pulse output                                    |

|    | KC04            | Out               | VOPKEY18      | -                   | Key Matrix scan pulse output                                    |

|    | KC05            | Out               | VOPKEY18      | -                   | Key Matrix scan pulse output                                    |

|    | KC06            | Out               | VOPKEY18      | -                   | Key Matrix scan pulse output                                    |

|    | KC07            | Out               | VOPKEY18      | -                   | Key Matrix scan pulse output                                    |

|    | KC08            | Out               | VOPKEY18      | -                   | Key Matrix scan pulse output                                    |

|    | KC09            | Out               | VOPKEY18      | -                   | Key Matrix scan pulse output                                    |

|    | KC10            | Out               | VOPKEY18      | -                   | Key Matrix scan pulse output                                    |

|    | KC11            | Out               | VOPKEY18      | -                   | Key Matrix scan pulse output                                    |

|    | VSS             | VSS               | -             | -                   |                                                                 |

|    | NC              | -                 | -             | -                   | Open                                                            |

|    | VDOUT12         | Out (Power)       | -             | -                   | Internally generated power output (for Internal circuit)        |

|    | INT             | In                | -             | -                   | GPIO(register data input)                                       |

|    | VOPSPI18        | In (Power)        | -             | Pull Down(6MΩ)      | Power input for SPI and GPIO (connect to pad37)                 |

|    | VDOUT18         | Out (Power)       | -             | -                   | Internally generated power output(for FeRAM)                    |

|    | NC              | -                 | -             | -                   | Open                                                            |

|    | NC              | -                 | -             | -                   | Open                                                            |

|    | PWRP3           | In                | -             | -                   | Antenna pad for external power supply                           |

| _  | PWRP1           | In                | -             | -                   | Antenna pad for RF communication                                |

|    | NC              | -                 | -             | -                   | Open                                                            |

| _  | PWRM1           | In                | -             | -                   | Antenna pad for RF communication                                |

|    | NC              | -                 | -             | -                   | Open                                                            |

|    | PWRM3           | In                | -             | -                   | Antenna pad for external power supply                           |

| _  | NC              | -                 | -             | -                   | Open                                                            |

|    |                 | -<br>Out (Device) | -             | -                   | Open<br>Dewar output for outprool dovises                       |

|    | VDOUT3<br>NC    | Out (Power)       | -             | -                   | Power output for external devices                               |

|    | VDIO            | -<br>Out (Power)  | -             | -                   | Open<br>IO Power output                                         |

|    | VDIO<br>VOPSPI3 | In (Power)        | -<br>VOPSPI3  | -<br>Pull Down(6MΩ) | Power output<br>Power input for SPI and GPIO (connect to Pad50) |

| _  | NC              | III (FOWEI)       | 1053513       |                     | Open                                                            |

|    | VDOUT18         | -<br>Out (Power)  | -<br>         | -                   | Internally generated power output(for FeRAM)                    |

|    | VOPKEY18        | In (Power)        | -<br>VOPKEY18 | -<br>Pull Down(6MΩ) | Power input for Key Matrix scan circuit (connect to pad53)      |

|    | KC12            | Out               | VOPKEY18      |                     | Key Matrix scan pulse output                                    |

|    | KC12<br>KC13    | Out               | VOPKEY18      | -                   | Key Matrix scan pulse output                                    |

|    | KC13<br>KC14    | Out               | VOPKEY18      | -                   | Key Matrix scan pulse output                                    |

|    | KC14<br>KC15    | Out               | VOPKEY18      | -                   | Key Matrix scan pulse output                                    |

|    | KR00            | In                | VOPKEY18      | Pull Down(150kO)    | Key Matrix scan buse output                                     |

|    | KR01            | In                | VOPKEY18      |                     | Key Matrix scan data input                                      |

|    | KR02            | In                | VOPKEY18      |                     | Key Matrix scan data input                                      |

|    | KR03            | In                | VOPKEY18      |                     | Key Matrix scan data input                                      |

|    | KR04            | In                | VOPKEY18      |                     | Key Matrix scan data input                                      |

|    | KR05            | In                | VOPKEY18      |                     | Key Matrix scan data input                                      |

|    | KR06            | In                | VOPKEY18      |                     | Key Matrix scan data input                                      |

|    | KR07            | In                | VOPKEY18      |                     | Key Matrix scan data input                                      |

|    | VSS             | VSS               | -             | -                   |                                                                 |

|    | VDOUT12         | Out (Power)       | -             | -                   | Internally generated power output (for Internal circuit)        |

|    |                 |                   |               |                     | , g                                                             |

#### Table 1.3.2.2 SPI pad status

|         | In             | itial | SPI Ma | ster(En=0) | SPI Ma  | ster(En=1) | SPI Slave |         |  |  |  |  |

|---------|----------------|-------|--------|------------|---------|------------|-----------|---------|--|--|--|--|

| PadName | e In/Out Value |       | In/Out | Value      | In/Out  | Value      | In/Out    | Value   |  |  |  |  |

| SPIREQ  | In             | —(PD) | In     | 0(PD)      | In      | 0(PD)      | In        | 1       |  |  |  |  |

| SPIACK  | Out            | L     | Out    | L          | Out     | L          | Out       | Н       |  |  |  |  |

| XCS     | In/Out         | HiZ   | Out    | HiZ        | Out     | H/L        | In        | 1/0     |  |  |  |  |

| SCK     | In/Out         | HiZ   | Out    | HiZ        | Out     | L/H        | In        | 0/1     |  |  |  |  |

| DI      | In             |       | In     | -          | In      | 0/1        | In        | 0/1     |  |  |  |  |

| DO      | Out            | HiZ   | Out    | HiZ        | Out     | L/H/HiZ    | Out       | L/H/HiZ |  |  |  |  |

| XRST    | Out            | L     | Out L  |            | Out L/H |            | Out       | _       |  |  |  |  |

\*. The initial state is reset state. SPI Master is in the state of SPI=L. SPI slave is in the state of SPIACK=H. Refer to Chapter 7.1.1 for SPI master setting (En=0/1).

(Information in the table) 0/1 : Input value, L/H : Output value, PD : PullDown, - : Invalid

. Ilivallu

Table 1.3.2.3 GPIO pad status

|         | In     | itial | Fur    | ncEn=0 | FuncEn=1 |             |  |  |

|---------|--------|-------|--------|--------|----------|-------------|--|--|

| PadName | In/Out | Value | In/Out | Value  | In/Out   | Value       |  |  |

| COM2-0  | Out    | HiZ   | Out    | HiZ    | Out      | L/H(ComDat) |  |  |

| INT     | In     | -     | In     | •      |          | 0/1         |  |  |

\*. Refer to Chapter 7.2.1 for GPIO setting (FuncEn=0/1)

Table 1.3.2.4 Key Matrix scan pad status

|           | In      | itial | KeyMat | rixscanOff | KeyMatrixscanON |         |  |  |

|-----------|---------|-------|--------|------------|-----------------|---------|--|--|

| PadName   | In/Out  | Value | In/Out | Value      | In/Out          | Value   |  |  |

| KC15-KC00 | Out     | HiZ   | Out    | HiZ        | Out             | HiZ/H   |  |  |

| KR07-KR00 | In –(PD |       | In     | —(PD)      | In              | 0(PD)/1 |  |  |

|           |         |       |        |            |                 |         |  |  |

\*. Refer to Chapter 7.3.1 for Key Matrix scan setting (Off/On).

## 1.4 POWER SUPPLY

This operational power is internally generated from RF power. For extended feature other than RFID tag feature, such as SPI Master, SPI Slave, and Key Matrix scan, the optional power (VOPSPI3, VOPSPI18, VOPKEY18, VOPKEY12) will be provided by connecting the designated pads as shown in Table 1.4.

Table 1.4 Power generation

| Extended Feature | Internal generated Power |              |                         | Optional Power |

|------------------|--------------------------|--------------|-------------------------|----------------|

|                  |                          | (Output pad) | $\overline{\mathbf{v}}$ | (Input pad)    |

| SPI Master       | 50                       | VDIO         | 51                      | VOPSPI3        |

|                  | 37                       | VDOUT18      | 36                      | VOPSPI18       |

| SPI Slave        | 50                       | VDIO         | 51                      | VOPSPI3        |

| SFISIAVE         | 37                       | VDOUT18      | 36                      | VOPSPI18       |

| Koy Matrix Soon  | 15                       | VDOUT12      | 14                      | VOPKEY12       |

| Key Matrix Scan  | 53                       | VDOUT18      | 54                      | VOPKEY18       |

#### 2 RF INTERFACE

RF signal interface is compliant with EPCglobal Class 1 Generation 2 Ver.1.2.0.

#### ■ 2.1 Modulation type, communications timing

Compliant with EPCglobal Class 1 Generation 2 Ver.1.2.0

## ■ 2.2 Inventory, Tag selection

Compliant with EPCglobal Class 1 Generation 2 Ver.1.2.0

#### ■ 2.3 Tag state-transition

Compliant with EPCglobal Class 1 Generation 2 Ver.1.2.0

### ■ 2.4 RF communication Error code

This LSI replies error code if it encounters an error when executing a handle-based command under Open state or Secured state. Error code described in EPCglobal Class 1 Generation 2 Ver.1.2.0 (AnnexI) and a proprietary error code are supported as shown in Table2.4.

| Table 2.4 Error code | ; |

|----------------------|---|

|----------------------|---|

| Error code | Error code name         | Error description                                            |

|------------|-------------------------|--------------------------------------------------------------|

| 00h        | Other errors            | Other errors not covered by the following errors             |

| 03h        | Memory overrun          | The specified memory location does not exist.                |

| 04h        | Memory locked           | The specified memory location is locked or permalocked       |

| 0Bh        | Insufficient power      | Insufficient power to perform the operation %1               |

| 8Eh        | No detection of Keys ※2 | No pressed key detected during the Key Matrix scan operation |

%1. This error covers not only RF command operation but also extended application (refer to Chapter 7). If the power is insufficient to backscatter, the LSI cannot reply error code,

\*2. Proprietary Error code for Key Matrix scan application

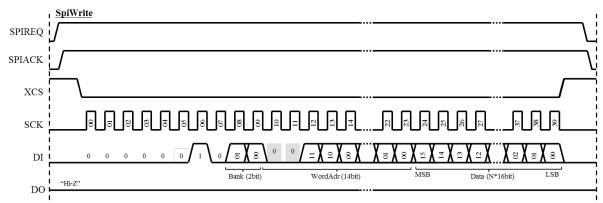

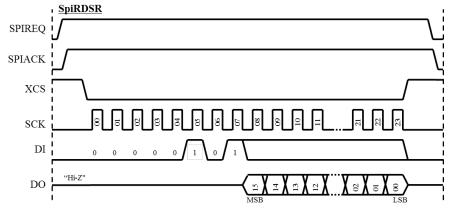

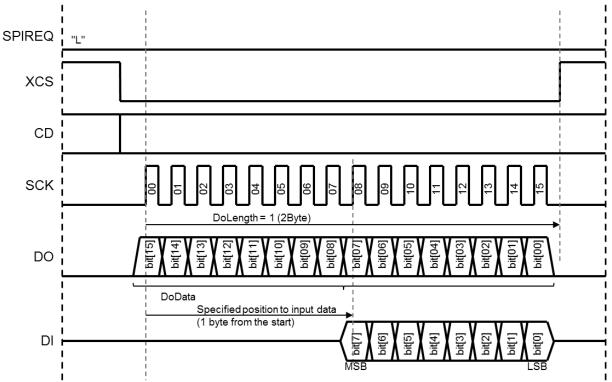

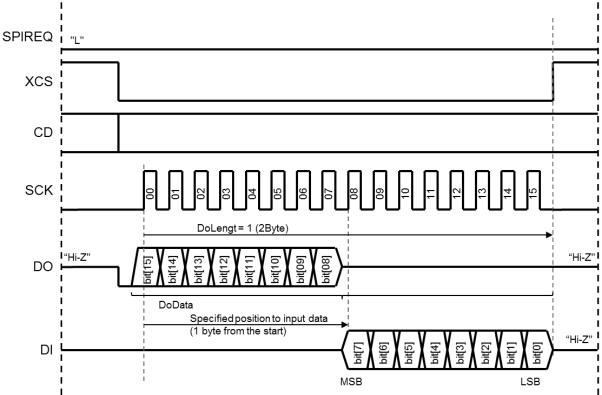

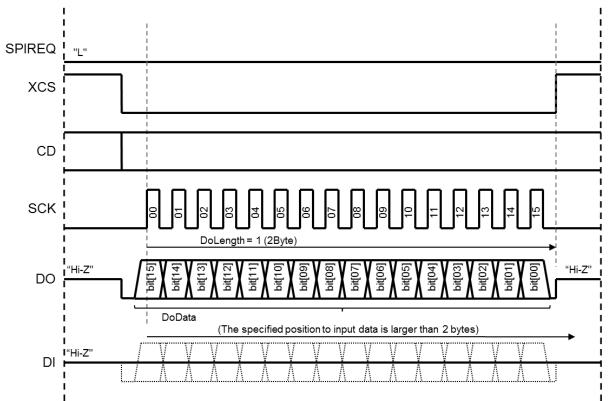

## ■ 3 SPI Interface

#### ■ 3.1 Overview

This LSI has SPI (Serial Peripheral Interface) interface that enables to operate the following features.

• As SPI slave device, the memory data can be accessed through the SPI interface (External power is required for the operation).

•As SPI master device, the external SPI slave device can be controlled by RF command (RF generated power is supplied for the external device).

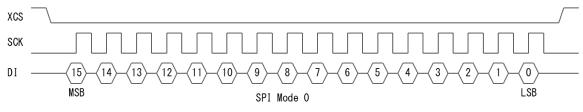

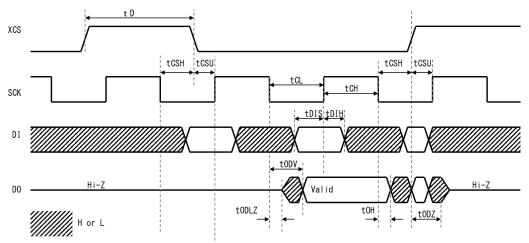

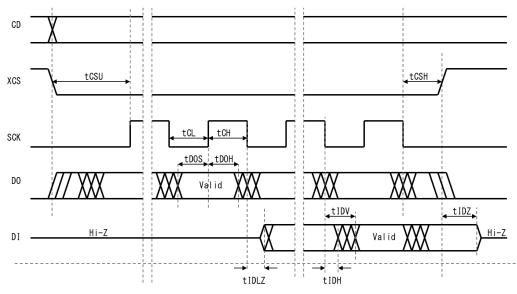

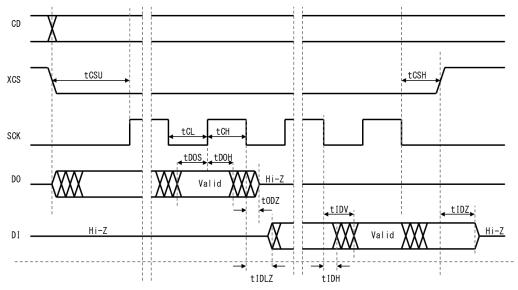

#### ■ 3.2 SPI Mode

This LSI supports SPI mode 0 (CPOL=0, CPHA=0).

Figure 3.2 – SPI mode

### ■ 3.3 SPI Slave Interface

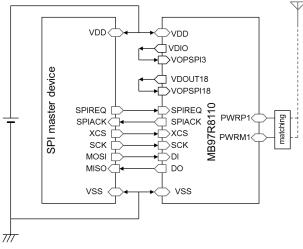

#### ■ 3.3.1 Connection to SPI Interface

When this LSI is used as SPI slave device, the connection with SPI controller (master) shall be as shown in Figure 3.3.1.

In order to start SPI slave communication, external SPI master device shall set SPIREQ to "H" level to request the communication. After SPIACK outputs "H" level, XCS shall be set to "L" level. And then SPI slave communication will be enabled. SPI controller shall stay SPIREQ "H" level, and can continue to execute commands without any interruption from RF interface during when SPIACK is "H" level. Any command from RF interface is invalid during SPI slave operation. When SPIACK is "L" level, SPI slave communication cannot be enabled.

Figure 3.3.1 - SPI Slave interface connection

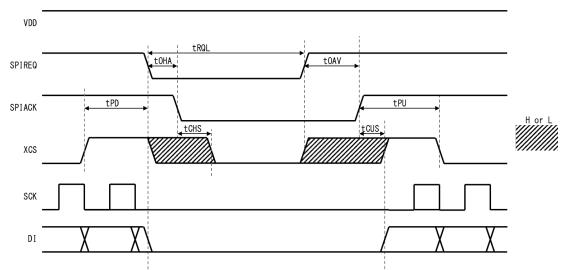

#### ■ 3.3.2 Power down mode

When SPI master operation is disabled, if SPIREQ is switched to "L" level, this LSI will be in power down mode, which enables to reduce current consumption between VDD-VSS. (refer to 8.4.1) All the input pins excepting VDD shall be "L" level during power down mode. When SPI master operation is enabled and SPIREQ is "L" level, it is prohibited to make XCS and SCK "L" level in order to avoid conflict with SPI master operation.

#### 3.3.3 Usage

Please refer to Chapter 5.2 and 5.3.regarding the usage of SPI slave interface.

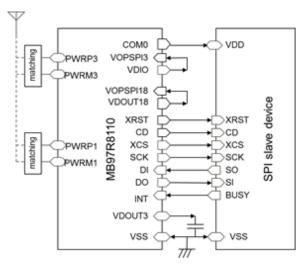

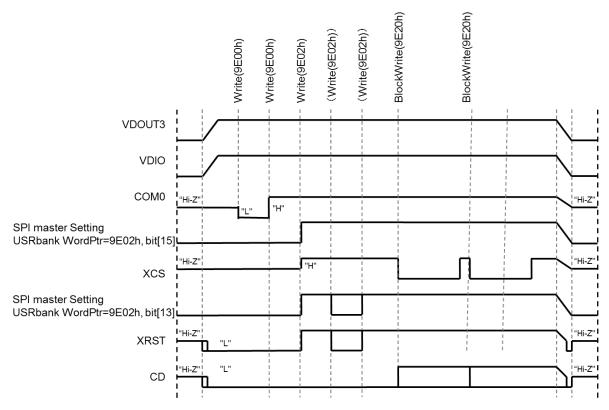

## ■ 3.4 SPI Master Interface

#### ■ 3.4.1 Connection to SPI Interface

When this LSI is used as SPI master device, the connection with external SPI slave device shall be as shown in Figure 3.4.1.1 and Figure 3.4.1.2. It is recommended to connect capacitor between VDOUT3 and VSS, when external SPI slave device operation causes rapid current consumption. And power supply to external SPI slave device is recommended to be controlled by "H" level output from any bit out of COM[2:0] of GPIO (refer to Chapter 7.2.1). VDIO output shall be connected to VOPSPI3, and VDOUT18 output shall be connected to VOPSPI18. In this case "H" level output of COM[2:0] will be the same as the voltage level input from VOPSPI3 (Refer to Chapter 7.1.7).

Figure 3.4.1.1 shows an example of SPI master interface connection, in which XRST and CD pins are used for the connection. And DI and DO are connected with external SPI slave device respectively. Busy signal of external SPI slave device is connected to INT pin, which is assigned in GPIO interface, and busy status can be read by Reader/Writer (refer to 7.2.2).

Figure 3.4.1.2 shows another example of SPI master interface connection, in which XRST, CD, and INT pins are not used for the connection. And DI and DO is used as common bus connection (Mux).

COM0 ססע VOPSPI3 PWRP3 VDIO WRM3 VOPSPI18 slave device VDOUT18 XRST CD MB97R8 XCS XCS WRD SCK SCK WRM1 R DI SIO DO INT VDOUT3 VSS VSS

Figure 3.4.1.1 - SPI master interface connection 1

Figure 3.4.1.2 - SPI master interface connection 2

#### 3.4.2 Usage

Please refer to Chapter 7.1 regarding the usage of SPI master interface.

## ■ 3.5 GPIO Interface

## ■ 3.5.1 GPIO

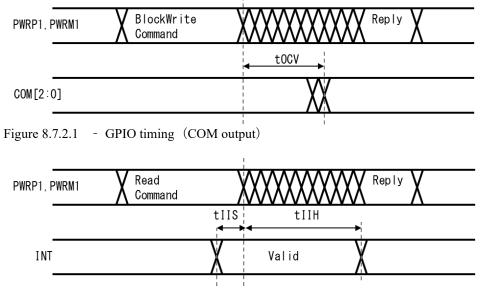

GPIO interface enables to output 3bits of register value to COM[2:0] pins (refer to chapter 4.2.4.2 about address allocation). The value can be updated by BlockWrite command of RF communication. The state of INT can be read by Read command of RF communication.

## ■ 3.5.2 Usage

GPIO can be utilized as the following use cases.

- LED ON/OFF control

- · Power supply to external SPI slave device under SPI master operation

- Status monitoring of external connected devices

For the detail, refer to Chapter 7.2.

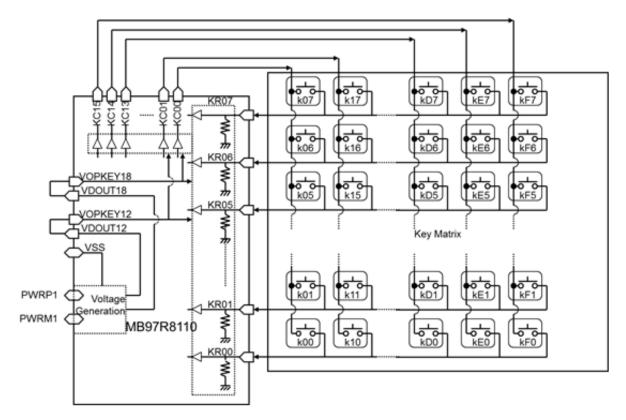

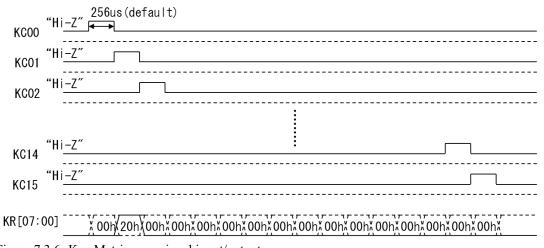

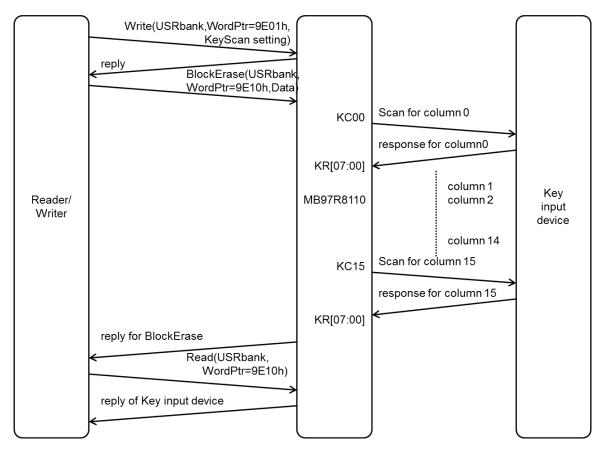

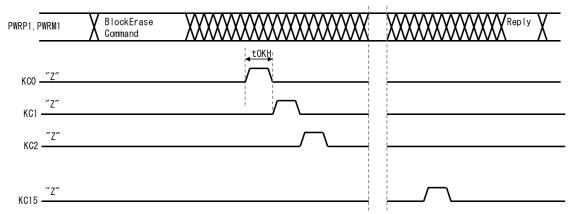

## ■ 3.6 Key Matrix scan interface

#### ■ 3.6.1 Connection method

The Key Matrix scan interface enables to be connected to matrix key input device which returns key data on scan clock.

Figure 3.6.1 – Key Matrix and connection example

#### ■ 3.6.2 Usage

Refer to Chapter 7.3 regarding the usage of Key Matrix scan interface

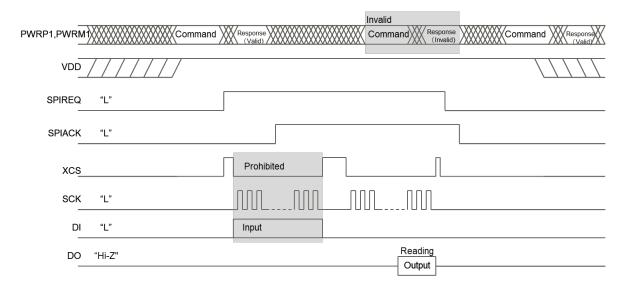

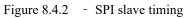

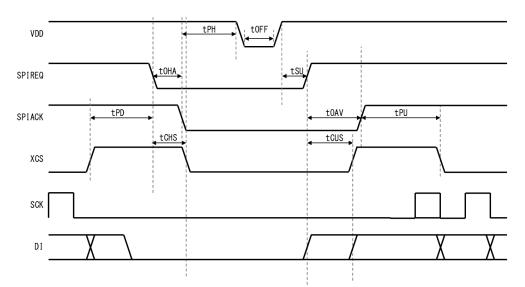

## ■ 3.7 Power sequence and Arbitration

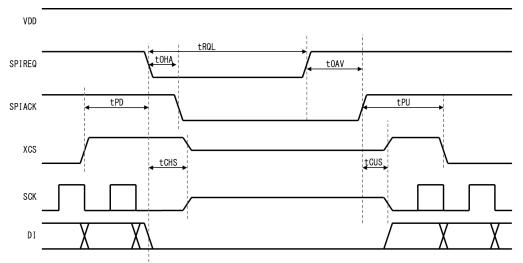

#### ■ 3.7.1 Arbitration between RF and SPI slave communication

The arbitration feature manages memory access from either RF interface or SPI interface in order to avoid any interruption to each other. SPIREQ and SPIACK manages to switch communication from RF interface to SPI interface by activating VDD, and vice versa.

In order to start SPI slave communication, the external SPI master device connected to this LSI shall set SPIREQ to "H" level to request communication. Upon the request, this LSI sets SPIACK to "H" level after completing active communication from RF interface. Then XCS shall be set to "L" level, and SPI slave communication will be ready. It is possible to start SPI slave communication during the period when SPIACK is "L" level, even if XCS is "L" level.

The example of arbitration sequence between RF and SPI slave communication is shown in Figure 3.7.1. As described, when SPIACK is "L" level, any command input from SPI slave interface is prohibited even if XCS is in "L" level. When SPIACK is "H" level, any command from RF interface is invalid and SPI slave communication will be continued. In this case, SPIREQ shall be set to "L" after completing active communication from SPI interface in order to switch to RF communication.

Figure 3.7.1 — The arbitration sequence between RF communication and SPI slave communication

In addition, SPI master function and Key Matrix scan function works as RF communication under the arbitration sequence above.

## ■ 4 Memory

## 4.1 Memory address

## 4.1.1 Address description

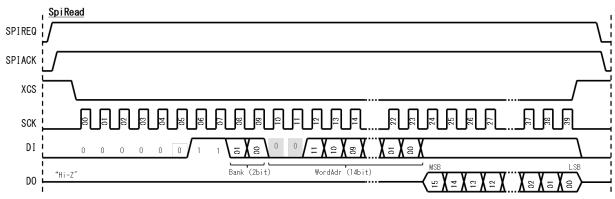

The memory address is allocated in the units of 16bits (=1word). The logical address in each memory bank is described as WordAdr in this document. WordPtr is the address specified by RF command access, which is described in EBV(Extensible bit vectors) format conforming to EPCglobal Class 1 Generation 2 standard (AnnexA). EBV format is shown in Talbe4.1.1. The address description in this document is shown in Table4.1.2. The address specified by SPI slave communication command from external SPI master device shall be 2bits of MemBank and 14bits of WordAdr(Total 16bits). The practical examples of the comparison between WordPtr and WordAdr are shown in Table4.1.3.

| Table 4.1.1 EBV format (Excerpt from | EPCglobal standard) |

|--------------------------------------|---------------------|

|--------------------------------------|---------------------|

|                     | 0     | 0 | 0000000 |   |         |   |         |

|---------------------|-------|---|---------|---|---------|---|---------|

|                     | 1     | 0 | 0000001 |   |         |   |         |

| 2 <sup>7</sup> – 1  | 127   | 0 | 1111111 |   |         |   |         |

| 2 <sup>7</sup>      | 128   | 1 | 0000001 | 0 | 0000000 |   |         |

| 2 <sup>14</sup> – 1 | 16383 | 1 | 1111111 | 0 | 1111111 |   |         |

| 2 <sup>14</sup>     | 16384 | 1 | 0000001 | 1 | 0000000 | 0 | 0000000 |

Table 4.1.2 Address description in this document

| Address range  | WordAdr[13:0]*1 | WordPtr[7:0] or<br>WordPtr[15:8]<br>(RF access) | Comparison between<br>WordPtr and WordAdr                        |

|----------------|-----------------|-------------------------------------------------|------------------------------------------------------------------|

| 0000h to 007Fh | 0000h to 007Fh  | 00h to 7Fh                                      | WordPtr={ <u>0</u> , WordAdr[6:0]} *2                            |

| 0080h to 0F3Fh | 0080h to 0F3Fh  | 8100h to 9E3Fh                                  | WordPtr={ <u>1</u> ,WordAdr[13:7],<br><u>0</u> ,WordAdr[6:0]} *2 |

\*1. The address specified by SPI slave access is 2bits of MemBank and 14bits of WordAdr (16bits total). \*2. Underlined 0,1 is defined by EBV format.

#### RAMXEED

Table 4.1.3 Comparison between WordPtr and WordAdr

| WordAdr = 0000h                                                                                                                                                                                                                             |                            |                       |                                                     |                                          |                                           |                                                  |                                                          |                                           |                            |                            |                                           |                            |                            |                                                          |                                 |                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------|-----------------------------------------------------|------------------------------------------|-------------------------------------------|--------------------------------------------------|----------------------------------------------------------|-------------------------------------------|----------------------------|----------------------------|-------------------------------------------|----------------------------|----------------------------|----------------------------------------------------------|---------------------------------|---------------------------------|

| WordAdr[13:0]                                                                                                                                                                                                                               | 1                          |                       | 13                                                  | 12                                       | 11                                        | 10                                               | 9                                                        | 8                                         | 7                          | 6                          | 5                                         | 4                          | 3                          | 2                                                        | 1                               | 0                               |

| 0000h                                                                                                                                                                                                                                       | †                          |                       | 0                                                   | 0                                        | 0                                         | 0                                                | 0                                                        | 0                                         | 0                          | 0                          | 0                                         | 0                          | 0                          | 0                                                        | 0                               | 0                               |

| 000011                                                                                                                                                                                                                                      |                            |                       |                                                     |                                          |                                           |                                                  | •                                                        |                                           | . •                        |                            |                                           |                            | , •                        |                                                          |                                 |                                 |

| WordPtr[7:0]                                                                                                                                                                                                                                | 1                          |                       |                                                     |                                          |                                           |                                                  |                                                          |                                           | 7                          | 6                          | 5                                         | 4                          | 3                          | 2                                                        | 1                               | 0                               |

| 00h                                                                                                                                                                                                                                         | †                          |                       |                                                     |                                          |                                           |                                                  |                                                          |                                           | 0                          | 0                          | 0                                         | 0                          | 0                          | 0                                                        | 0                               | 0                               |

|                                                                                                                                                                                                                                             |                            |                       |                                                     |                                          | (                                         | 6                                                |                                                          |                                           |                            |                            |                                           |                            | , •                        |                                                          |                                 |                                 |

| SPI Slave address[15:0                                                                                                                                                                                                                      | 15                         | 14                    | 13                                                  | 12                                       | 11                                        | 10                                               | 9                                                        | 8                                         | 7                          | 6                          | 5                                         | 4                          | 3                          | 2                                                        | 1                               | 0                               |

| 0000h                                                                                                                                                                                                                                       | Mem                        | Bank                  | 0                                                   | 0                                        | 0                                         | 0                                                | 0                                                        | 0                                         | 0                          | 0                          | 0                                         | 0                          | 0                          | 0                                                        | 0                               | 0                               |

|                                                                                                                                                                                                                                             |                            |                       |                                                     |                                          | -                                         |                                                  | -                                                        |                                           |                            | -                          |                                           |                            |                            |                                                          |                                 |                                 |

| WordAdr = 007Fh                                                                                                                                                                                                                             |                            |                       |                                                     |                                          |                                           |                                                  |                                                          |                                           |                            |                            |                                           |                            |                            |                                                          |                                 |                                 |

| WordAdr[13:0]                                                                                                                                                                                                                               | 1                          |                       | 13                                                  | 12                                       | 11                                        | 10                                               | 9                                                        | 8                                         | 7                          | 6                          | 5                                         | 4                          | 3                          | 2                                                        | 1                               | 0                               |

| 007Fh                                                                                                                                                                                                                                       | +                          |                       | 0                                                   | 0                                        | 0                                         | 0                                                | 0                                                        | 0                                         | 0                          | 1                          | 1                                         | 1                          | 1                          | 1                                                        | 1                               | 1                               |

|                                                                                                                                                                                                                                             |                            |                       |                                                     |                                          |                                           |                                                  |                                                          |                                           |                            |                            |                                           |                            |                            |                                                          |                                 |                                 |

| WordPtr[7:0]                                                                                                                                                                                                                                | 1                          |                       |                                                     |                                          |                                           |                                                  |                                                          |                                           | 7                          | 6                          | 5                                         | 4                          | 3                          | 2                                                        | 1                               | 0                               |

| 7Fh                                                                                                                                                                                                                                         | +                          |                       |                                                     |                                          |                                           |                                                  |                                                          |                                           | 0                          | 1                          | 1                                         | 1                          | 1                          | 1                                                        | 1                               | 1                               |

|                                                                                                                                                                                                                                             |                            |                       |                                                     | !                                        |                                           | <u> </u>                                         |                                                          |                                           | 0                          | -                          |                                           | , •                        |                            | •                                                        |                                 |                                 |

| SPI Slave address[15:0                                                                                                                                                                                                                      | 1 15                       | 14                    | 13                                                  | 12                                       | 11                                        | 10                                               | 9                                                        | 8                                         | 7                          | 6                          | 5                                         | 4                          | 3                          | 2                                                        | 1                               | 0                               |

| 0000h                                                                                                                                                                                                                                       | Mem                        |                       | 0                                                   | 0                                        |                                           | -                                                | -                                                        | -                                         |                            | -                          |                                           |                            |                            | _                                                        |                                 |                                 |

|                                                                                                                                                                                                                                             | mon                        | Dalin                 | U                                                   | U                                        | 0                                         | 0                                                | 0                                                        | 0                                         | 0                          | 1                          | 1                                         | 1                          | 1                          | 1                                                        | 1                               | 1                               |

| WordAdr = 0080h                                                                                                                                                                                                                             | 1                          | Daim                  |                                                     |                                          |                                           |                                                  | -                                                        |                                           |                            |                            |                                           |                            |                            | -                                                        | ,                               |                                 |

| WordAdr = 0080h<br>WordAdr[13:0]                                                                                                                                                                                                            |                            | Dank                  | 13                                                  | 12                                       | 11                                        | 10                                               | 9                                                        | 8                                         | 7                          | 6                          | 5                                         | 4                          | 3                          | 2                                                        | 1                               | 0                               |

| WordAdr = 0080h                                                                                                                                                                                                                             |                            |                       |                                                     |                                          |                                           |                                                  | -                                                        |                                           |                            |                            |                                           |                            |                            | -                                                        | ,                               |                                 |

| WordAdr = 0080h<br>WordAdr[13:0]<br>0080h                                                                                                                                                                                                   |                            |                       | 13<br>0                                             | 12<br>0                                  | 11<br>0                                   | 10<br>0                                          | 9<br><b>0</b>                                            | 8<br>0                                    | 7                          | 6<br>0                     | 5<br>0                                    | 4                          | 3                          | 2                                                        | 1<br>0                          | 0                               |

| WordAdr = 0080h<br>WordAdr[13:0]<br>0080h<br>WordPtr[15:0]                                                                                                                                                                                  | 15                         | 14                    | 13<br><b>0</b><br>13                                | 12<br>0<br>12                            | 11<br>0<br>11                             | 10<br><b>0</b><br>10                             | 9<br><b>0</b><br>9                                       | 8<br><b>0</b><br>8                        | 7 1 7                      | 6<br>0<br>6                | 5<br><b>0</b><br>5                        | 4<br>0<br>4                | 3<br>0<br>3                | 2<br>0<br>2                                              | 1<br>0<br>1                     | 0<br>0                          |

| WordAdr = 0080h<br>WordAdr[13:0]<br>0080h                                                                                                                                                                                                   |                            |                       | 13<br>0                                             | 12<br>0                                  | 11<br>0                                   | 10<br>0                                          | 9<br><b>0</b>                                            | 8<br>0                                    | 7                          | 6<br>0                     | 5<br>0                                    | 4                          | 3                          | 2                                                        | 1<br>0                          | 0                               |

| WordAdr = 0080h<br>WordAdr[13:0]<br>0080h<br>WordPtr[15:0]<br>8100h                                                                                                                                                                         | 15                         | 14<br>0               | 13<br>0<br>13<br>0                                  | 12<br>0<br>12<br>0                       | 11<br>0<br>11<br>0                        | 10<br>0<br>10<br>0                               | 9<br>0<br>9<br>0                                         | 8<br>0<br>8<br>1                          | 7<br>1<br>7<br>0           | 6<br>0<br>6<br>0           | 5<br>0<br>5<br>0                          | 4                          | 3<br>0<br>3<br>0           | 2<br>0<br>2<br>0                                         | 1<br>0<br>1<br>0                | 0<br>0<br>0<br>0                |

| WordAdr = 0080h<br>WordAdr[13:0]<br>0080h<br>WordPtr[15:0]<br>8100h<br>SPI Slave address[15:0]                                                                                                                                              | 15<br>1<br>1<br>1<br>15    | 14<br>0<br>14         | 13<br>0<br>13<br>0<br>13                            | 12<br>0<br>12<br>0                       | 11<br>0<br>11<br>0                        | 10<br><b>0</b><br>10<br><b>0</b><br>10           | 9<br>0<br>9<br>0                                         | 8<br>0<br>8<br>1                          | 7<br>1<br>7<br>0<br>7      | 6<br>0<br>6<br>0           | 5<br>0<br>5<br>0                          | 4<br>0<br>4<br>0           | 3<br>0<br>3<br>0           | 2<br>0<br>2<br>0                                         | 1<br>0<br>1<br>0                | 0<br>0<br>0<br>0                |

| WordAdr = 0080h<br>WordAdr[13:0]<br>0080h<br>WordPtr[15:0]<br>8100h                                                                                                                                                                         | 15                         | 14<br>0<br>14         | 13<br>0<br>13<br>0                                  | 12<br>0<br>12<br>0                       | 11<br>0<br>11<br>0                        | 10<br>0<br>10<br>0                               | 9<br>0<br>9<br>0                                         | 8<br>0<br>8<br>1                          | 7<br>1<br>7<br>0           | 6<br>0<br>6<br>0           | 5<br>0<br>5<br>0                          | 4                          | 3<br>0<br>3<br>0           | 2<br>0<br>2<br>0                                         | 1<br>0<br>1<br>0                | 0<br>0<br>0<br>0                |

| WordAdr = 0080h<br>WordAdr[13:0]<br>0080h<br>WordPtr[15:0]<br>8100h<br>SPI Slave address[15:0]                                                                                                                                              | 15<br>1<br>1<br>1<br>15    | 14<br>0<br>14         | 13<br>0<br>13<br>0<br>13                            | 12<br>0<br>12<br>0                       | 11<br>0<br>11<br>0                        | 10<br><b>0</b><br>10<br><b>0</b><br>10           | 9<br>0<br>9<br>0                                         | 8<br>0<br>8<br>1                          | 7<br>1<br>7<br>0<br>7      | 6<br>0<br>6<br>0           | 5<br>0<br>5<br>0                          | 4<br>0<br>4<br>0           | 3<br>0<br>3<br>0           | 2<br>0<br>2<br>0                                         | 1<br>0<br>1<br>0                | 0<br>0<br>0<br>0                |

| WordAdr = 0080h<br>WordAdr[13:0]<br>0080h<br>WordPtr[15:0]<br>8100h<br>SPI Slave address[15:0]<br>0080h<br>WordAdr = 0F3Fh<br>WordAdr[13:0]                                                                                                 | 15<br>1<br>1<br>1<br>15    | 14<br>0<br>14         | 13<br>0<br>13<br>0<br>13                            | 12<br>0<br>12<br>0                       | 11<br>0<br>11<br>0                        | 10<br><b>0</b><br>10<br><b>0</b><br>10           | 9<br>0<br>9<br>0                                         | 8<br>0<br>8<br>1                          | 7<br>1<br>7<br>0<br>7      | 6<br>0<br>6<br>0           | 5<br>0<br>5<br>0                          | 4<br>0<br>4<br>0           | 3<br>0<br>3<br>0           | 2<br>0<br>2<br>0                                         | 1<br>0<br>1<br>0                | 0<br>0<br>0<br>0                |

| WordAdr = 0080h<br>WordAdr[13:0]<br>0080h<br>WordPtr[15:0]<br>8100h<br>SPI Slave address[15:0]<br>0080h<br>WordAdr = 0F3Fh                                                                                                                  | 15<br>1<br>1<br>1<br>15    | 14<br>0<br>14         | 13<br>0<br>13<br>0<br>13<br>0                       | 12<br>0<br>12<br>0                       | 11<br>0<br>11<br>0<br>11<br>0             | 10<br>0<br>10<br>0                               | 9<br>0<br>9<br>0<br>9<br>0                               | 8<br>0<br>8<br>1<br>8<br>0                | 7<br>1<br>7<br>0<br>7<br>1 | 6<br>0<br>6<br>0           | 5<br>0<br>5<br>0<br>5<br>0                | 4<br>0<br>4<br>0           | 3<br>0<br>3<br>0<br>3<br>0 | 2<br>0<br>2<br>0                                         | 1<br>0<br>1<br>0                | 0<br>0<br>0<br>0<br>0           |

| WordAdr = 0080h<br>WordAdr[13:0]<br>0080h<br>WordPtr[15:0]<br>8100h<br>SPI Slave address[15:0]<br>0080h<br>WordAdr = 0F3Fh<br>WordAdr[13:0]                                                                                                 | 15<br>1<br>1<br>1<br>15    | 14<br>0<br>14         | 13<br>0<br>13<br>0<br>13<br>0<br>13                 | 12<br>0<br>12<br>0<br>12<br>0            | 11<br>0<br>11<br>0<br>11<br>0             | 10<br>0<br>10<br>0<br>10<br>0                    | 9<br>0<br>9<br>0<br>9<br>0                               | 8<br>0<br>1<br>8<br>0                     | 7<br>1<br>7<br>0<br>7<br>1 | 6<br>0<br>6<br>0<br>0      | 5<br>0<br>5<br>0<br>5<br>0                | 4<br>0<br>4<br>0<br>4<br>0 | 3<br>0<br>3<br>0<br>3<br>0 | 2<br>0<br>2<br>0                                         | 1<br>0<br>1<br>0<br>1<br>0      | 0<br>0<br>0<br>0<br>0           |

| WordAdr = 0080h<br>WordAdr[13:0]<br>0080h<br>WordPtr[15:0]<br>8100h<br>SPI Slave address[15:0]<br>0080h<br>WordAdr = 0F3Fh<br>WordAdr[13:0]                                                                                                 | 15<br>1<br>1<br>1<br>15    | 14<br>0<br>14         | 13<br>0<br>13<br>0<br>13<br>0<br>13                 | 12<br>0<br>12<br>0<br>12<br>0            | 11<br>0<br>11<br>0<br>11<br>0             | 10<br>0<br>10<br>0<br>10<br>0                    | 9<br>0<br>9<br>0<br>9<br>0                               | 8<br>0<br>1<br>8<br>0                     | 7<br>1<br>7<br>0<br>7<br>1 | 6<br>0<br>6<br>0<br>0      | 5<br>0<br>5<br>0<br>5<br>0                | 4<br>0<br>4<br>0<br>4<br>0 | 3<br>0<br>3<br>0<br>3<br>0 | 2<br>0<br>2<br>0                                         | 1<br>0<br>1<br>0<br>1<br>0      | 0<br>0<br>0<br>0<br>0           |

| WordAdr = 0080h           WordAdr[13:0]           0080h           WordPtr[15:0]           8100h           SPI Slave address[15:0]           0080h           WordAdr = 0F3Fh           WordAdr[13:0]           0F3Fh                         | 15<br>1<br>Mem             | 14<br>0<br>14<br>Bank | 13<br>0<br>13<br>0<br>13<br>0<br>13<br>0            | 12<br>0<br>12<br>0<br>12<br>0            | 11<br>0<br>11<br>0<br>11<br>0             | 10<br>0<br>10<br>0<br>10<br>0                    | 9<br>0<br>9<br>0<br>9<br>0<br>9<br>0                     | 8<br>0<br>1<br>8<br>0<br>8<br>1           | 7<br>1<br>7<br>0<br>7<br>1 | 6<br>0<br>6<br>0<br>0      | 5<br>0<br>5<br>0<br>5<br>0                | 4<br>0<br>4<br>0<br>4<br>0 | 3<br>0<br>3<br>0<br>3<br>0 | 2<br>0<br>2<br>0<br>2<br>0                               | 1<br>0<br>1<br>0                | 0<br>0<br>0<br>0<br>0           |

| WordAdr = 0080h           WordAdr[13:0]           0080h           WordPtr[15:0]           8100h           SPI Slave address[15:0]           0080h           WordAdr = 0F3Fh           WordAdr[13:0]           0F3Fh           WordPtr[15:0] | 15<br>1<br>15<br>Mem       | 14<br>0<br>14<br>Bank | 13<br>0<br>13<br>0<br>13<br>0<br>13<br>0<br>13<br>0 | 12<br>0<br>12<br>0<br>12<br>0<br>12<br>0 | 11<br>0<br>11<br>0<br>11<br>11<br>1<br>11 | 10<br>0<br>10<br>0<br>10<br>10<br>10<br>10<br>10 | 9<br>0<br>9<br>0<br>9<br>0<br>0<br>9<br>0<br>1<br>9<br>9 | 8<br>0<br>1<br>8<br>0<br>8<br>1<br>8<br>8 | 7<br>1<br>7<br>0<br>7<br>1 | 6<br>0<br>6<br>0<br>6<br>0 | 5<br>0<br>5<br>0<br>5<br>0<br>5<br>1<br>5 | 4<br>0<br>4<br>0<br>4<br>0 | 3<br>0<br>3<br>0<br>3<br>0 | 2<br>0<br>2<br>0<br>2<br>0<br>2<br>1<br>2<br>2<br>2<br>1 | 1<br>0<br>1<br>0<br>1<br>1<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0 |

| WordAdr = 0080h           WordAdr[13:0]           0080h           WordPtr[15:0]           8100h           SPI Slave address[15:0]           0080h           WordAdr = 0F3Fh           WordAdr[13:0]           0F3Fh           WordPtr[15:0] | 15<br>1<br>15<br>Mem<br>15 | 14<br>0<br>14<br>Bank | 13<br>0<br>13<br>0<br>13<br>0<br>13<br>0<br>13<br>0 | 12<br>0<br>12<br>0<br>12<br>0<br>12<br>0 | 11<br>0<br>11<br>0<br>11<br>11<br>1<br>11 | 10<br>0<br>10<br>0<br>10<br>10<br>10<br>10<br>10 | 9<br>0<br>9<br>0<br>9<br>0<br>0<br>9<br>0<br>1<br>9<br>9 | 8<br>0<br>1<br>8<br>0<br>8<br>1<br>8<br>8 | 7<br>1<br>7<br>0<br>7<br>1 | 6<br>0<br>6<br>0<br>6<br>0 | 5<br>0<br>5<br>0<br>5<br>0<br>5<br>1<br>5 | 4<br>0<br>4<br>0<br>4<br>0 | 3<br>0<br>3<br>0<br>3<br>0 | 2<br>0<br>2<br>0<br>2<br>0<br>2<br>1<br>2<br>2<br>2<br>1 | 1<br>0<br>1<br>0<br>1<br>1<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0 |

\* The data stored in bit15, bit7 of WordPtr is defined by EBV format.

## ■ 4.2 Memory Map

#### ■ 4.2.1 Memory bank

The Non-volatile memory (FeRAM) of this LSI is divided into the following four banks.

Table 4.2.1 Memory map

| E                | Bank       | Add            | Command Accessibility |          |                      |            |            |                      |          |             |           |  |

|------------------|------------|----------------|-----------------------|----------|----------------------|------------|------------|----------------------|----------|-------------|-----------|--|

| MemBank<br>[1:0] | Definition | WordAdr[13:0]  | WordPtr[15:8]         | RF       |                      |            |            |                      |          |             | SPI Slave |  |

|                  |            |                | WordPtr[7:0]          | Read     | Write                | BlockWrite | BlockErase | BlockPermalock       | Select   | SpiRead     | SpiWrite  |  |

| 11               | USER       | 0000h to 0EFFh | 00h to 9D7Fh          | <b>~</b> | <ul> <li></li> </ul> | <b>~</b>   | <b>~</b>   | <ul> <li></li> </ul> | <b>~</b> | <b>&gt;</b> | <b>~</b>  |  |

| 11               | USER       | 0F00h to 0F3Fh | 9E00h to 9E3Fh        | >        | <                    | ∕*         | ∕*         |                      | >        | >           | _         |  |

| 10               | TID        | 0000h to 000Ch | 00h to 0Ch            | <        |                      |            |            |                      | <        | >           |           |  |

| 01               | EPC        | 0000h to 001Fh | 00h to 1Fh            | <        | <                    | >          | <          | _                    | >        | >           | -         |  |

| 00               | RESERVED   | 0000h to 003Fh | 00h to 3Fh            | >        | <b>&gt;</b>          |            | -          | —                    |          | -           | —         |  |

\*. The command works for executing extended application on some specific address.

USER, TID, EPC, and RESERVED memory banks contain the data in the format defined by EPCglobal C1G2 specification (Chapter 6.3.2.1). In each memory bank, the WordAdr and the WordPtr start from zero (00h).

## ■ 4.2.2 TID bank

The memory map of TID bank is shown in Table 4.2.2. TID bank can only be read, and the setting values cannot be changed. For details, please refer to EPCglobal Class 1 Generation 2 standard.

|         |         | MSB         |                             |       |        |       |      |      |      |     |   | L | _SB    | 5                |

|---------|---------|-------------|-----------------------------|-------|--------|-------|------|------|------|-----|---|---|--------|------------------|

| WordAdr | WordPtr | 15 14 13 12 | 11 10                       | 9     | 8      | 7     | 6    | 5    | 4    | 3   | 2 | 1 | 0      | Setting<br>Value |

| 00h     | 00h     | Allocatio   | on Class                    |       |        |       |      | D    | esig | ner |   |   |        | E281h            |

| 01h     | 01h     | Designer    | Designer Product ID Version |       |        |       |      |      |      |     |   |   | 0081h  |                  |

| 02h     | 02h     |             |                             |       |        |       |      |      |      |     |   |   | 3C00h  |                  |

| 03h     | 03h     |             |                             | Seria | al Nu  | umbe  | ər   |      |      |     |   |   |        | unique           |

| 04h     | 04h     |             |                             |       |        |       |      |      |      |     |   |   | unique |                  |

| 05h     | 05h     |             |                             | Seria | al Nu  | umbe  | er   |      |      |     |   |   |        | unique           |

| 06h     | 06h     |             | option                      | al co | mm     | and   | supp | oort |      |     |   |   |        | 1DDEh            |

| 07h     | 07h     |             | Blo                         | ckEra | ase    | para  | mete | ər   |      |     |   |   |        | 0002h            |

| 08h     | 08h     |             | Blo                         | ckEra | ase    | para  | mete | ər   |      |     |   |   |        | 0310h            |

| 09h     | 09h     |             | Blo                         | ckWı  | rite p | barar | nete | r    |      |     |   |   |        | 0002h            |

| 0Ah     | 0Ah     |             | BlockWrite parameter        |       |        |       |      |      |      |     |   |   | 0310h  |                  |

| 0Bh     | 0Bh     |             | Per                         | malc  | ock E  | Block | siz  | e    |      |     |   |   |        | 0200h            |

| 0Ch     | 0Ch     |             | User memory size            |       |        |       |      |      |      |     |   |   | 0F00h  |                  |

Table 4.2.2 TID bank memory map

#### ■ 4.2.3 EPC bank

The memory map of EPC bank is shown in Table 4.2.3.

|         |         | MSB |    |    |    |    |     |      |       |       |      |      |   |   |   | l | LSB | 5                |

|---------|---------|-----|----|----|----|----|-----|------|-------|-------|------|------|---|---|---|---|-----|------------------|

| WordAdr | WordPtr | 15  | 14 | 13 | 12 | 11 | 10  | 9    | 8     | 7     | 6    | 5    | 4 | 3 | 2 | 1 | 0   | Default<br>Value |

| 00h     | 00h     |     |    |    |    |    |     | Sto  | ored  | CRC   | ;    |      |   |   |   |   |     |                  |

| 01h     | 01h     |     |    |    |    |    |     | S    | tored | I PC  |      |      |   |   |   |   |     | 3400h            |

| 02h     | 02h     |     |    |    |    |    |     | E    | PC o  | lata  |      |      |   |   |   |   |     | 0000h            |

| 03h     | 03h     |     |    |    |    | E  | EPC | data | Seri  | al Nu | ımbe | er*) |   |   |   |   |     | unique           |

| 04h     | 04h     |     |    |    |    | E  | EPC | data | Seri  | al Nu | Imbe | er*) |   |   |   |   |     | unique           |

| 05h     | 05h     |     |    |    |    | E  | EPC | data | Seri  | al Nu | ımbe | er*) |   |   |   |   |     | unique           |

| 06h     | 06h     |     |    |    |    |    |     | E    | PC o  | lata  |      |      |   |   |   |   |     | 0000h            |

| 07h     | 07h     |     |    |    |    |    |     | E    | PC o  | lata  |      |      |   |   |   |   |     | 0000h            |

| 08h     | 08h     |     |    |    |    |    |     | E    | PC o  | lata  |      |      |   |   |   |   |     | 0000h            |

| 09h     | 09h     |     |    |    |    |    |     | E    | PC o  | lata  |      |      |   |   |   |   |     | 0000h            |

| 0Ah     | 0Ah     |     |    |    |    |    |     | E    | PC o  | lata  |      |      |   |   |   |   |     | 0000h            |

| 0Bh     | 0Bh     |     |    |    |    |    |     | E    | PC o  | lata  |      |      |   |   |   |   |     | 0000h            |

| 0Ch     | 0Ch     |     |    |    |    |    |     | E    | PC o  | lata  |      |      |   |   |   |   |     | 0000h            |

| 0Dh     | 0Dh     |     |    |    |    |    |     | E    | PC o  | lata  |      |      |   |   |   |   |     | 0000h            |

| 0Eh     | 0Eh     |     |    |    |    |    |     | E    | PC o  | lata  |      |      |   |   |   |   |     | 0000h            |

| 0Fh     | 0Fh     |     |    |    |    |    |     | E    | PC o  | lata  |      |      |   |   |   |   |     | 0000h            |

| 10h     | 10h     |     |    |    |    |    |     | E    | PC o  | lata  |      |      |   |   |   |   |     | 0000h            |

|         |         |     |    |    |    |    |     | E    | PC o  | lata  |      |      |   |   |   |   |     | 0000h            |

| 1Fh     | 1Fh     |     |    |    |    |    |     | E    | PC d  | lata  |      |      |   |   |   |   |     | 0000h            |

Table 4.2.3 EPC bank memory map

\*. As default value, the same serial number is stored in WordAdr=03h to 05h of EPC bank as the number stored in WordAdr=03h to 05h of TID bank.

The length of EPC is specified by EPC length field of Stored PC. The length is preprogrammed to 6 (words) as default value, which indicates 6words of EPC (WordAdr 02h to 07h). It is possible to expand the length up to 30words (WordAdr 02h to 1Fh) by programming the data of EPC length field

This LSI does not support XPC\_W1 and XPC\_W2. Stored CRC is not preprogrammed, because it is reflected after the response to ACK command.

#### ■ 4.2.4 USER bank

USER bank of this LSI consists of 3,840words of Data field and 64words of Application field.

## ■ 4.2.4.1 USER bank (Data field)

Data field of USER bank is divided into 8 Area groups as shown in Table.4.2.4.1.

|              | MSB LSB        |    |                      |                      |    |    |    |      |      |      |     |       | 3 |   |       |   |   |                  |

|--------------|----------------|----|----------------------|----------------------|----|----|----|------|------|------|-----|-------|---|---|-------|---|---|------------------|

| WordAdr      | WordPtr        | 15 | 14                   | 13                   | 12 | 11 | 10 | 9    | 8    | 7    | 6   | 5     | 4 | 3 | 2     | 1 | 0 | Default<br>Value |

| 000h to 1FFh | 00h to 837Fh   |    |                      | User data (Area0) 00 |    |    |    |      |      |      |     |       |   |   | 0000h |   |   |                  |

| 200h to 3FFh | 8400h to 877Fh |    |                      |                      |    |    | ι  | Jser | data | (Are | a1) |       |   |   |       |   |   | 0000h            |

| 400h to 5FFh | 8800h to 8B7Fh |    |                      |                      |    |    | ι  | Jser | data | (Are | a2) |       |   |   |       |   |   | 0000h            |

| 600h to 7FFh | 8C00h to 8F7Fh |    |                      |                      |    |    | ι  | Jser | data | (Are | a3) |       |   |   |       |   |   | 0000h            |

| 800h to 9FFh | 9000h to 937Fh |    |                      |                      |    |    | ι  | Jser | data | (Are | a4) |       |   |   |       |   |   | 0000h            |

| A00h to BFFh | 9400h to 977Fh |    |                      |                      |    |    | ι  | Jser | data | (Are | a5) |       |   |   |       |   |   | 0000h            |

| C00h to DFFh | 9800h to 9B7Fh |    | User data (Area6) 00 |                      |    |    |    |      |      |      |     | 0000h |   |   |       |   |   |                  |

| E00h to EFFh | 9C00h to 9D7Fh |    |                      |                      |    |    | l  | Jser | data | (Are | a7) |       |   |   |       |   |   | 0000h            |

Table 4.2.4.1 USER bank (Data field) memory map

Each area can be protected by Area Password (refer to Chapter6.2). And the same area is allocated for PermalockBlock (refer to Chapter5.1.3).

Regarding the memory access from RF communication (BlockWrite, BlockErase, and Read command), when the address reaches to WordPtr=8F7Fh (WordAdr=7FFh) among the range specified by WordCount, the address

to be followed will be WordPtr=9000h (WordAdr=800h). In the same case from SPI slave communication (SpiWrite, SpiRead command), the address counter rollovers from WordAdr=7FFh to 000h.

## ■ 4.2.4.2 USER bank (Application field)

Application field of USER bank allocated in WordPtr=9E00h to 9E3Fh (WordAdr=F00h to F3Fh) is used for the extensive applications described in Chapter 7, which consists of 16bit registers, command control, and data storage. This field is writable only from RF interface. The registers located in WordPtr=9E00h to 9E03h

(WordAdr=F00h to F03h) are volatile, and the stored value will be reset to "0", if the internal voltage drops below the lower limit. Memory map of the field is shown in Table.4.2.4.2. The data stored in WordPtr=9E10h to 9E13h (WordAdr=F10h to F13h) are non-volatile and they are updated with the latest data. The area located in WordPtr=9E2xh and 9E3xh (WordAdr=F2xh and F3xh), which is allocated for SPI master application, consists of volatile memory and non-volatile memory.

|         | MSB     |     |                         |       |      |       |      |      |       |       |            |      | L    | LSB   |        |          |    |       |               |

|---------|---------|-----|-------------------------|-------|------|-------|------|------|-------|-------|------------|------|------|-------|--------|----------|----|-------|---------------|

| WordAdr | WordDtr | 15  | 11                      | 12    | 10   | 11    | 10   | 9    | 8     | 7     | 6          | 5    | 4    | 3     | 2      | 1        | 0  | Reset | Volatile      |

| voruAu  | wordPit | 15  | 14                      | 13    | 12   | 11    | 10   | 9    | 0     | 1     | 0          | 5    | 4    | 3     | 2      | 1        | 0  | Value | /Non-Volatile |

| F00h    | 9E00h   |     |                         |       |      |       |      | GP   | IO S  | ettir | ng         |      |      |       |        |          |    | 0000h | Volatile      |

| F01h    | 9E01h   |     | Key Matrix scan setting |       |      |       |      |      |       |       |            |      |      |       | 0000h  | Volatile |    |       |               |

| F02h    | 9E02h   |     | SPI Master setting      |       |      |       |      |      |       |       |            |      |      |       | 0000h  | Volatile |    |       |               |

| F03h    | 9E03h   |     |                         |       |      |       | ١    | /DO  | UT3   | set   | ting       |      |      |       |        |          |    | 0000h | Volatile      |

| F04h    | 9E04h   |     |                         |       |      |       |      | R    | eser  | ved   |            |      |      |       |        |          |    | 0000h |               |

| F05h    | 9E05h   |     |                         |       |      |       |      | R    | eser  | ved   |            |      |      |       |        |          |    | 0000h |               |

|         |         |     |                         |       |      |       |      | R    | eser  | ved   |            |      |      |       |        |          |    | 0000h |               |

| F0Fh    | 9E0Fh   |     |                         |       |      |       |      | R    | eser  | ved   |            |      |      |       |        |          |    | 0000h |               |

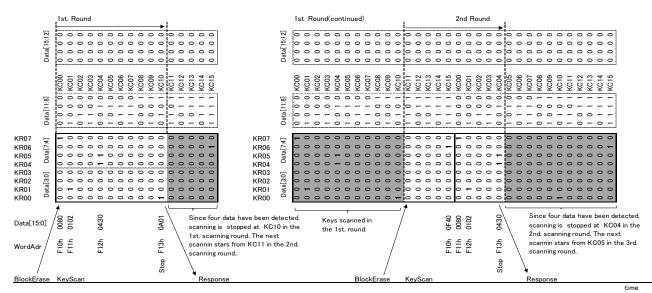

| F10h    | 9E10h   | Key | Ма                      | atrix | scar | l col | mma  | nd c | ontro | ol ar | nd Pr      | esse | ed K | ey c  | lata l | buffe    | er | 0000h | Non-Volatile  |

| F11h    | 9E11h   |     |                         |       |      |       | Pres | sed  | Key   | data  | a buf      | fer  |      |       |        |          |    | 0000h | Non-Volatile  |

| F12h    | 9E12h   |     |                         |       |      |       | Pres | sed  | Key   | data  | ata buffer |      |      |       |        |          |    | 0000h | Non-Volatile  |

| F13h    | 9E13h   |     |                         |       |      |       | Pres | sed  | Key   | data  | a buf      | fer  |      |       |        |          |    | 0000h | Non-Volatile  |

| F14h    | 9E14h   |     |                         |       |      |       |      | R    | eser  | ved   |            |      |      |       |        |          |    | 0000h |               |

|         |         |     | Reserved                |       |      |       |      |      |       |       | 0000h      |      |      |       |        |          |    |       |               |

| F1Fh    | 9E1Fh   |     | Reserved                |       |      |       |      |      |       |       |            |      |      | 0000h |        |          |    |       |               |

| F2xh    | 9E2xh   |     | Application area        |       |      |       |      |      |       |       |            |      |      |       | 0000h  | -        |    |       |               |

| F3xh    | 9E3xh   |     | Application area        |       |      |       |      |      |       |       |            |      |      |       | 0000h  | -        |    |       |               |

Table 4.2.4.2 USER bank (Application field) memory map

## ■ 4.2.5 RESERVED bank

RESERVED bank is used for Password data management.

32bits Password can be set by 2steps of 16bits writing, 1st for [31:16] and 2nd for [15:0] by Req\_RN and Write command as a set of sequence respectively without any other command between the steps.

| Table 4.2.5 RESERVED b | bank memory map |

|------------------------|-----------------|

|------------------------|-----------------|

|         |         | MSB |      |       | -    | -     |       |        |        |       |      |    |   |       |    | L | .SB | J.               |

|---------|---------|-----|------|-------|------|-------|-------|--------|--------|-------|------|----|---|-------|----|---|-----|------------------|

| WordAdr | WordPtr | 15  | 14   | 13    | 12   | 11    | 10    | 9      | 8      | 7     | 6    | 5  | 4 | 3     | 2  | 1 | 0   | Default<br>Value |

| 00h     | 00h     |     |      |       |      |       | K     | ill pa | sswo   | ord   |      |    | [ | 31:16 | 6] |   |     | 0000h            |

| 01h     | 01h     |     |      |       |      |       | K     | ill pa | sswo   | ord   |      |    | [ | 15:0] |    |   |     | 0000h            |

| 02h     | 02h     |     |      |       |      | A     | Acces | s pa   | sswo   | ord   |      |    | [ | 31:16 | 6] |   |     | 0000h            |

| 03h     | 03h     |     |      |       |      | A     | Acces | s pa   | sswo   | ord   |      |    | ] | 15:0] |    |   |     | 0000h            |

| 04h     | 04h     |     |      |       |      |       |       | R      | eser   | ved   |      |    |   |       |    |   |     | 0000h            |

|         |         |     |      |       |      |       |       |        |        |       |      |    |   |       |    |   |     | 0000h            |