產品技術延伸 Tech Column

FeRAM 原理全解析:從基本結構到非揮発性記憶體的優勢比較

FeRAM 是一種非揮發性記憶體,同時具備揮發性記憶體的優點。除了在電源關閉後資料仍可保存的非揮發特性外,還擁有高寫入耐久性與高速寫入能力。以下將說明 FeRAM 的特性、原理以及基本動作機制。

FeRAM 的特性

FeRAM(Ferroelectric Random Access Memory)是一種非揮發性記憶體,同時融合了揮發性記憶體的性能優勢。作為非揮發性記憶體,其特點包括即使電源關閉資料仍可保存(非揮發性)以及低功耗運作;同時也具備揮發性記憶體所具有的高寫入耐久性(可承受大量寫入次數)與高速寫入能力,因此可歸納為具備上述四大特性的記憶體。表 1 顯示 FeRAM 與其他記憶體產品的特性比較。FeRAM 採用鐵電材料作為記憶元件,透過製程技術的持續開發,已實現超過 100 兆次的寫入耐久性以及可對應 125°C 高溫環境的性能。

表 1.記憶體特性比較

FeRAM 的原理

FeRAM 採用強誘電體材料 PZT(鉛鋯鈦酸鹽,Lead Zirconate Titanate)作為記憶元件。其 PZT 的晶體結構如圖 1 所示。PZT 晶體的特性在於,當施加電壓時會產生極化現象(Zr/Ti 原子在晶體內部上下位移),即使停止施加電壓後極化狀態仍會殘留。因此,依據電場方向的不同,原子會形成兩個穩定狀態,並將其作為非揮發性記憶體中的「0」與「1」資料儲存原理。

圖 1.PZT(鉛鋯鈦酸鹽)的晶體結構

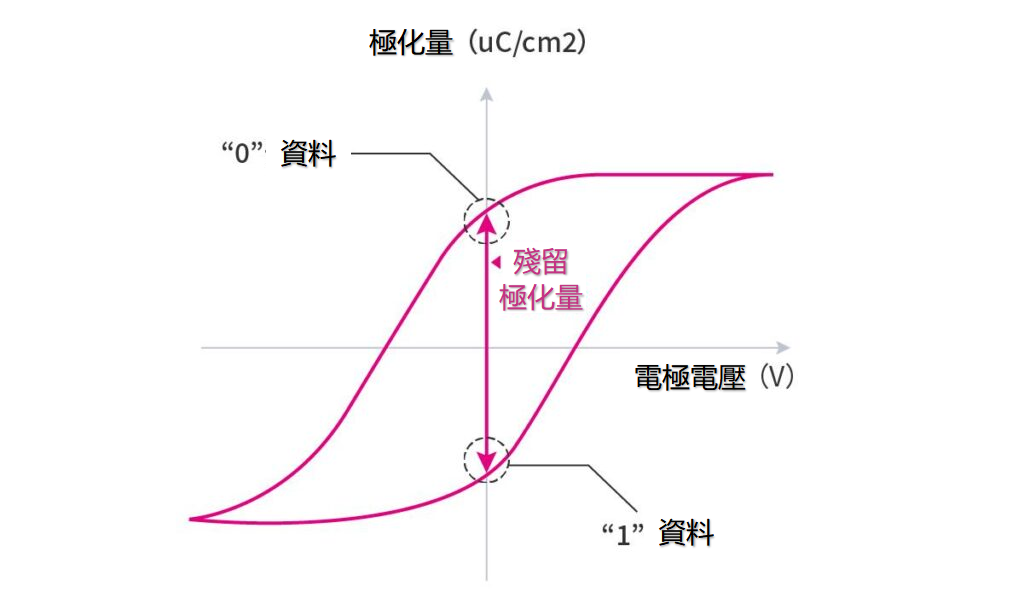

PZT 晶體的極化量與電壓關係特性如圖 2 所示。其極化量呈現遲滯(Hysteresis)特性,在電壓為 0V 時存在兩個穩定點,並分別對應為「0」與「1」資料。由於 Zr/Ti 原子在晶體內部上下移動時產生的物理損傷極小,因此形成具備極高寫入耐久性的記憶元件。此外,在進行寫入時,不受先前穩定狀態(「0」或「1」資料)影響,僅需改變電場方向即可轉換至下一個穩定狀態(「0」或「1」資料),因此在特性比較表中以「可重複覆寫(Overwrite)」來表達此特性。

圖 2.PZT 晶體極化量與電壓特性(遲滯特性)

FeRAM 的記憶體單元結構

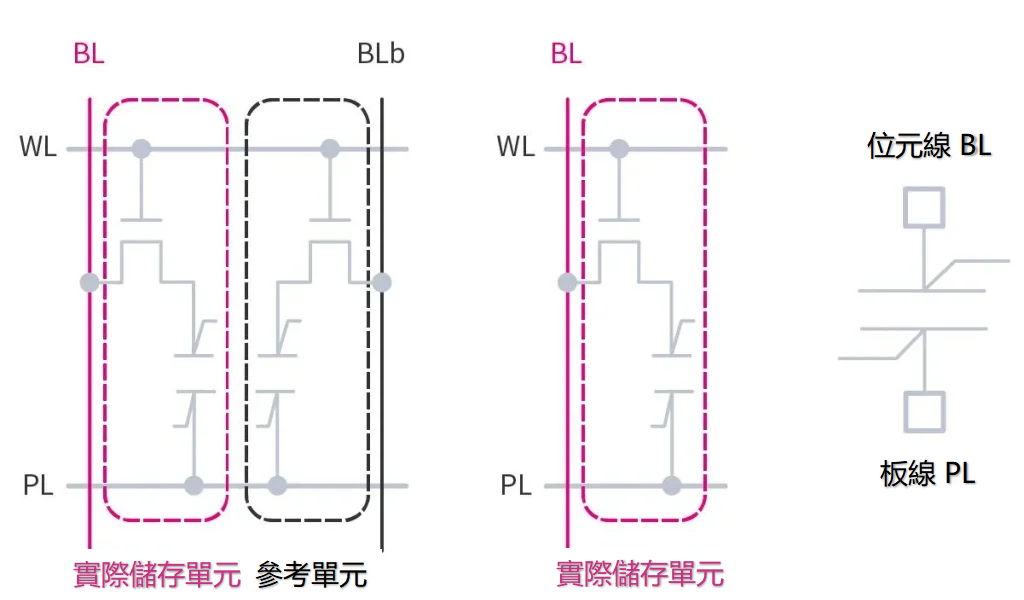

FeRAM 的記憶體單元結構主要分為兩種類型:一種是每個單元由 2 個電晶體與 2 個強誘電體電容構成的 2T2C 型(圖 3),另一種是每個單元由 1 個電晶體與 1 個強誘電體電容構成的 1T1C 型(圖 4)。強誘電體電容是指以強誘電體材料夾在導電體(上電極與下電極)之間形成的電容結構,各導電體分別連接至位元線(BL)與板極線(PL)(圖 5)。

圖 3.2T2C 型記憶體單元結構 圖 4.1T1C 型記憶體單元結構 圖 5.強誘電體電容結構

2T2C 型是將實際單元與參考單元相鄰配置,並使參考單元保持與實際單元相反的資料狀態進行電路運作。透過比較實際單元輸出的位元線電壓(BL)與參考單元輸出的位元線電壓(BLb)來判斷資料內容,當 BL > BLb 時判定為「1」資料,當 BL < BLb 時判定為「0」資料。由於兩個強誘電體電容以互補方式運作,使資料保持更為穩定,因此常應用於車用電子等高可靠性需求產品。

1T1C 型則是將實際單元輸出的位元線電壓(BL)與由獨立電路產生的參考電壓進行比較,當 參考電壓 > BL 時判定為「1」資料,當 參考電壓 < BL 時判定為「0」資料。由於單一記憶體單元面積僅為 2T2C 型的一半,因此特別適合應用於大容量 FeRAM 產品設計。

FeRAM 的基本動作

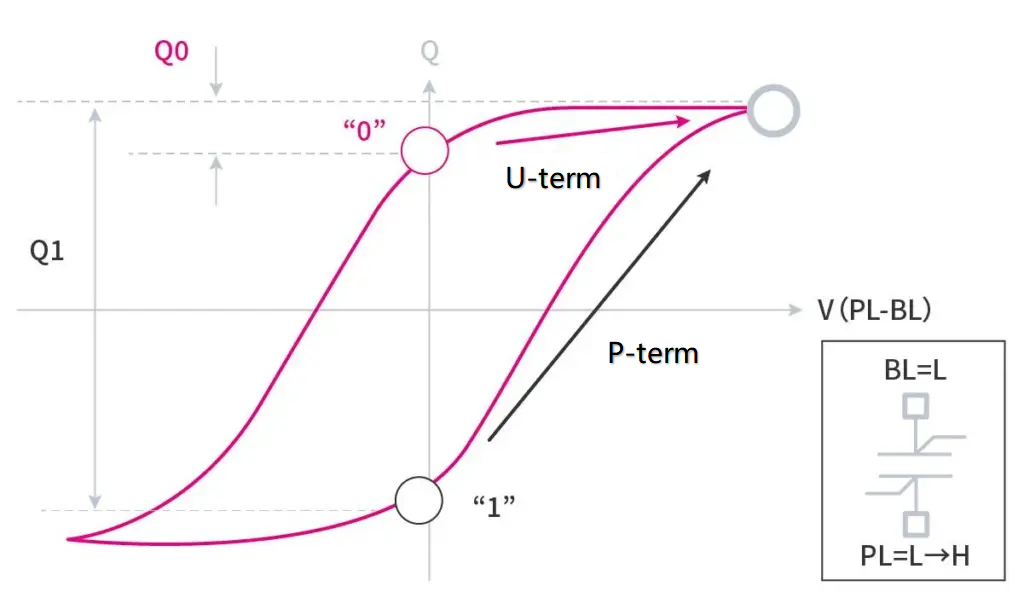

記憶體單元的讀取(Read)動作如圖 6 所示。當將連接至強誘電體電容位元線(BL)的電極設為 Low,並將連接至板極線(PL)的電極電壓由 Low 提升至 High(BL=L,PL=L→H) 時,即可進行讀取動作。在 PL=L→H 的過程中,原本儲存在強誘電體中的電荷會被釋放,而依據穩定狀態(「0」「1」資料)不同,所輸出的電荷量 Q 亦有所差異。透過偵測此電荷量差異來判斷「0」「1」資料,於電路層級上則表現為位元線上的電位差,並經由感測放大器(Sense Amplifier)放大後輸出為資料訊號。

圖 6.記憶體單元讀取動作(遲滯特性轉換)

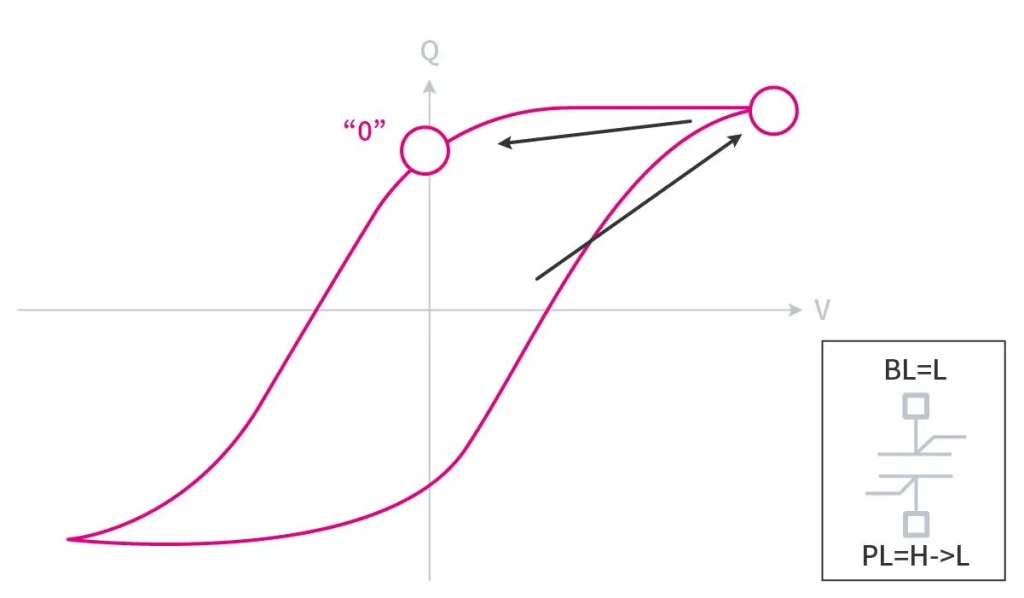

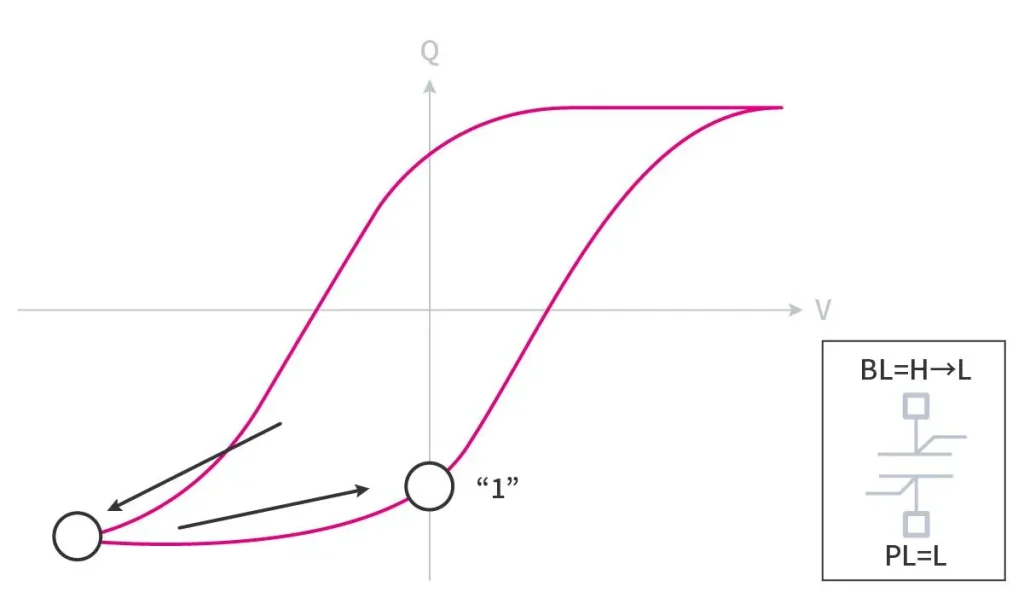

記憶體單元的寫入(Write)動作如圖 7、圖 8 所示。當寫入「0」資料時,將連接至強誘電體電容位元線(BL)的電極設為 Low,並將連接至板極線(PL)的電極施加 High 電壓(BL=L,PL=H) 以完成寫入動作,之後再將板極線(PL)拉回 Low,使其進入待機狀態並以「0」資料保持。另一方面,當寫入「1」資料時,將連接至位元線(BL)的電極設為 High,並將連接至板極線(PL)的電極設為 Low(BL=H,PL=L) 以完成寫入動作,之後再將位元線(BL)拉回 Low,使其進入待機狀態並以「1」資料保持。

圖 7.記憶體單元寫入動作(遲滯特性轉換):「0」資料情況

圖 8.記憶體單元寫入動作(遲滯特性轉換):「1」資料情況