EEPROMの寿命を延ばすウェアレベリング技術:基本から実装手法、代替技術まで

EEPROMの寿命を延ばすウェアレベリング技術について、基礎から実装例、代替技術であるFeRAMまでを詳しく解説します。設計エンジニアの課題解決に役立つ内容を紹介します。

目次

はじめに:EEPROMとウェアレベリングの重要性

EEPROMは、不揮発性でありながら繰り返し書き換えが可能なメモリとして多くの組み込みシステムで採用されています。しかし、EEPROMには書き換え可能な回数に物理的な限界が存在し、特定セルへの集中的なアクセスが寿命の偏りを生む要因となります。この課題を解決するために、「ウェアレベリング」と呼ばれる技術が重要な役割を果たします。本記事では、このウェアレベリング技術の基礎から実装手法、さらにはそれを不要とする代替技術までを解説し、設計エンジニアに向けた実用的な知見を提供します。

EEPROMの基本特性と書き換え回数の制限

EEPROMは電源を切ってもデータを保持できる不揮発性メモリであり、比較的小容量ながらも低消費電力と柔軟なデータアクセス性が求められるアプリケーションに適しています。一方、EEPROMには書き込み耐性の限界があり、一般的に10万回〜100万回程度の書き換えが上限とされます。このため、頻繁にアクセスされるデータ領域が偏ると、その部分のセルが早期に劣化し、エラーやデータ損失の原因となります。

ウェアレベリングの必要性とその効果

ウェアレベリングは、書き換え対象のメモリセルを分散させることで、すべてのセルに均等な負荷を与える技術です。これにより、特定領域の早期劣化を防ぎ、EEPROM全体としての寿命を延ばすことが可能となります。特に設定情報やログデータの保存など、頻繁な書き込みが発生する場面では、ウェアレベリングが信頼性向上の鍵となります。加えて、製品の長寿命化や保守頻度の削減にも貢献します。

ウェアレベリングの基本概念と種類

ウェアレベリングには、設計手法や目的に応じて複数のアプローチが存在します。大きく分けると「動的ウェアレベリング」「静的ウェアレベリング」「グローバルウェアレベリング」という三つの手法が知られており、それぞれ特徴や適用範囲が異なります。どの手法を選ぶかは、システムのメモリ使用パターン、データの更新頻度、設計上の制約などによって判断されます。

動的ウェアレベリング(Dynamic Wear Leveling)

動的ウェアレベリングは、主に書き込み操作時にのみメモリセルの寿命分散を図る方式です。未使用または使用頻度の低いセルへ書き込みを割り当て、消去可能な範囲で効率的に書き換え回数を均等化します。動的手法は実装が比較的容易であり、限られたリソースでも効果を得やすいのが特徴です。ただし、既にデータが存在するセルの扱いが課題となり、長期間にわたり静的なデータが配置された領域の劣化防止には対応が困難な場合があります。

静的ウェアレベリング(Static Wear Leveling)

静的ウェアレベリングでは、動的手法に加えて、データが存在するすべてのセルの使用状況を定期的に監視・評価し、使用頻度に応じてデータの再配置を行います。これにより、書き換えが発生しにくい静的データ領域にも適度にアクセスが加わり、全体の寿命をさらに均等化することが可能です。ただし、実装には高度な管理アルゴリズムとリソースが必要であり、制御ソフトウェアの設計が複雑化する傾向にあります。

グローバルウェアレベリング(Global Wear Leveling)

グローバルウェアレベリングは、メモリ全体を対象として寿命均等化を徹底的に行う手法です。データ構造やアクセスロジックを含む全領域に対して、書き換え履歴や使用状況を追跡・記録し、全体最適化を目指すアプローチです。この方式は最も高い寿命均等化効果を得られる一方で、管理データの保存領域や処理コストが増加し、システム全体の設計に強く影響します。

実装手法と注意点:ウェアレベリングの仕組みと応用

ウェアレベリングの概念を理解したうえで、具体的な実装方法を知ることは、実際のシステム設計において非常に有用です。多くの組み込みシステムでは、EEPROMの代替としてフラッシュメモリを用いたエミュレーションや、制御ソフトウェアによる寿命分散処理が採用されています。この章では、特定の製品名に依存せずに、一般的に用いられているウェアレベリングの実装手法や設計上の注意点について解説します。

書き込み履歴の分散によるセル保護手法

ウェアレベリングを実現する基本的な考え方は、同一アドレスに繰り返し書き込むのではなく、物理的に異なるメモリ領域へデータを逐次移動させることです。前回のデータに上書きせず、次の空き領域へ書き込み、有効なデータを追跡する仕組みによって、特定セルへの集中を避け、書き換え寿命の均等化が図れます。

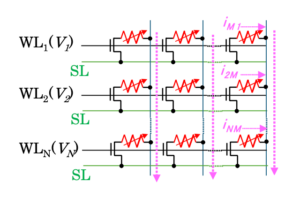

フラッシュメモリ領域の管理アルゴリズム

EEPROMエミュレーションでは、メモリを複数セクタに分割し、それぞれの書き換え回数を追跡します。セクタ単位でのガベージコレクション、書き込み対象の選定、消去スケジューリングを組み合わせたアルゴリズムが必要です。これにより、使用頻度の偏りを抑え、全体のバランスを保ちながら寿命を延ばすことができます。

書き換え回数を均一化するデータ構造と手法

書き換え回数の管理には、カウンタやCRCを組み込んだデータ構造が使われます。書き込み時には最新データとその整合性情報を記録し、読み出し時には最も信頼性の高いデータを抽出します。この手法により、電源断などの異常時にも整合性を維持しつつ、書き換え履歴の記録と再利用を効率的に行えます。

ウェアレベリングの課題と限界

ウェアレベリングはEEPROMの信頼性と寿命を向上させる上で有効な手法ですが、その実装や運用にはいくつかの技術的課題と制約が伴います。設計エンジニアは、システムの要求とリソース制限を考慮しながら、実装の複雑化、リソース消費、そして電源障害時のリスクへの対策を講じる必要があります。この章では、ウェアレベリング技術が直面する代表的な問題点について解説し、設計段階で注意すべき観点を提示します。

ソフトウェア実装の複雑性とリソース消費

ウェアレベリングを効果的に機能させるためには、メモリの使用状況を追跡し、書き込み対象を動的に管理する制御ロジックが不可欠です。このため、ファームウェアは通常よりも複雑化し、設計・テスト・デバッグにかかる工数が増大します。また、管理情報を保存するために追加のメモリ領域を確保する必要があり、特にリソース制約の厳しい小規模なマイコン環境では実装が困難になることもあります。メモリと処理能力のバランスを見極めることが肝要です。

消去サイクル管理とその最適化の難しさ

EEPROMやフラッシュメモリは、書き込み前に消去処理が必要な場合が多く、この消去操作もまた回数に制限があります。ウェアレベリングを行う際には、書き込み位置を変えるだけでなく、古いデータ領域の適切なタイミングでの消去と再利用が求められます。消去サイクルが最適に管理されていないと、空き領域が不足したり、過剰な書き換えが一部領域に集中したりするリスクがあります。このため、消去処理のスケジューリングやガベージコレクションの設計が重要な課題となります。

電源断時におけるデータ保護の工夫と制限

EEPROMやエミュレーションフラッシュでは、書き込みや消去の途中で電源が遮断されると、データの不整合が発生する可能性があります。特にウェアレベリングを行っている場合、データが複数領域に分散されているため、整合性の検証がより複雑になります。一般的には、書き込み前後にフラグやチェックサムを利用した対策が取られますが、それでも完全な保護は難しく、ハードウェア側での電源保持やバックアップ機構といった補完手段を検討する必要があります。

代替技術:FeRAMによるウェアレベリング不要のメモリ設計

EEPROMやフラッシュメモリの寿命や書き換え制限に対して、近年注目されているのがFeRAM(FRAM、強誘電体メモリ)です。FeRAMは不揮発性でありながら、高速で高耐久な書き換えが可能な次世代メモリとして、ウェアレベリングを必要としないシステム設計を実現します。この章では、FeRAMの基本特性からウェアレベリングが不要となる理由、設計エンジニアにとっての利点までを詳しく解説します。

FeRAMの書き換え耐性と高速性の特長

FeRAMは、強誘電体材料の分極反転を利用してデータを記憶する不揮発性メモリです。その大きな特長の一つが、書き換え回数の多さであり、一般的なEEPROMが10万~100万回程度であるのに対し、FeRAMは1兆回以上の書き換え耐性を持ちます。さらに、書き込み速度も高速で、数十ナノ秒というオーダーで動作可能です。これにより、頻繁にデータ更新を行うアプリケーションでも性能低下や信頼性の問題を引き起こさずに済みます。

ウェアレベリング不要の設計がもたらす利点

FeRAMは高い書き換え耐性を持つため、特定のセルに集中してデータを書き込んでも劣化の心配が少なく、ウェアレベリング処理をソフトウェアで実装する必要がありません。これにより、ファームウェア設計が大幅に簡素化され、リソースや工数の削減が実現できます。また、ウェアレベリングによる追加メモリ領域の確保も不要となるため、限られたメモリ資源を有効に使うことが可能です。開発期間の短縮やシステム全体の信頼性向上にもつながります。

設計エンジニアにとっての実装容易性と将来性

設計エンジニアにとって、FeRAMの最大の魅力は「使いやすさ」にあります。アドレス指定によるランダムアクセスが可能でありながら、書き換え頻度を気にせずに運用できるため、設計の自由度が高まります。さらに、低消費電力で動作し、動作温度範囲も広いことから、過酷な環境下でも信頼性の高いデータ保持が可能です。今後、IoTや産業機器、車載用途などにおいて、FeRAMは従来のEEPROMやフラッシュメモリに代わる選択肢として、ますます注目されていくでしょう。

まとめと今後の展望

EEPROMは多くの組み込みシステムにおいて信頼性と柔軟性を両立する不揮発性メモリとして広く利用されていますが、その書き換え寿命には限界があります。これを補う技術としてウェアレベリングは有効な手法であり、設計上の工夫により寿命の偏りを軽減することが可能です。一方で、その実装にはリソースや開発工数の負担が伴い、電源喪失時の整合性確保といった課題も存在します。近年では、FeRAMなどの新しい不揮発性メモリ技術の登場により、ウェアレベリング不要な設計が現実味を帯びてきており、今後の選択肢として注目されています。

ウェアレベリング技術の価値と適用範囲の理解

ウェアレベリングは、EEPROMやフラッシュメモリの限られた書き換え寿命を最大限に活かすための重要な技術です。特に、頻繁に設定情報やログデータを書き込む用途において、メモリの寿命を平準化する効果があります。システム要件や使用パターンに応じて、動的・静的・グローバルの各手法を適切に選定することで、バランスの取れた設計が可能となります。技術者にとっては、まずこの技術の意義と適用条件を正しく理解することが重要です。

要件に応じた適切な不揮発性メモリの選択

すべての用途においてウェアレベリングを適用すべきとは限らず、要件に応じたメモリ選定が求められます。例えば、書き換え頻度が低く、長期間のデータ保持が求められるアプリケーションでは、従来型のEEPROMが適しています。一方で、高頻度なデータ更新が求められる場合には、ウェアレベリングを実装するか、あるいはFeRAMのような高耐久な不揮発性メモリを採用する方が合理的です。設計初期段階での要件分析が選定のカギとなります。

不揮発性メモリ技術の今後の発展と可能性

FeRAMをはじめとする新世代不揮発性メモリは、従来の技術的制約を克服しつつあります。加えて、MRAMやReRAMといった他の技術も台頭しており、それぞれに特長があります。今後、より多様な不揮発性メモリが実用化される中で、設計者は各技術の特性やコスト、信頼性を評価し、最適な組み込み方法を検討する必要があります。メモリ技術の進化に対応し、柔軟かつ持続可能なシステム設計ができることが今後の鍵となります。