アナログASIC設計におけるLDOレギュレーターの役割と高性能化手法

センサー向けアナログASICにおけるLDOレギュレーターの役割や設計手法を解説します。ノイズ対策や電源安定化、高PSRR化など高性能化のポイントと実装時の評価・設計上の注意点について詳しく紹介しています。

センサー応用におけるアナログASICの役割と設計概論

近年のセンサーシステムは、単なるデータ取得デバイスから、高度なセンシングと情報処理を統合したインテリジェントな構成へと進化しています。この中でアナログASICは、センサからの微弱信号を取り込み、ノイズを排除しつつ正確に処理するための中核技術として重要な位置を占めています。汎用ICでは対応しきれない特性を持つセンサーも多く、それぞれのセンサー仕様や使用環境に応じたカスタム回路の設計が求められています。アナログASICの導入により、センサーの性能を最大限に引き出しながら、機器の小型化・低消費電力化・信頼性向上を同時に実現することが可能になります。

センサーシステムにおけるアナログASICの必要性とは

センサーシステムにおいてアナログASICは、信号の取り込みから初期処理までを担う重要な役割を果たします。特に微小なアナログ信号を高精度に取り扱うには、汎用ICでは対応しきれないノイズ特性や電源条件への最適化が不可欠です。アナログASICは、センサー特性や動作環境に合わせた専用回路設計が可能で、性能・小型化・消費電力のバランスを高次元で実現できます。さらに、センサーから取得する信号の信頼性確保にも直結するため、製品の品質に大きな影響を及ぼします。

アナログASICに求められる性能要件(ノイズ耐性・分解能・電源安定性)

アナログASIC設計においては、主にノイズ耐性の確保、信号分解能の向上、そして電源の安定性が重要な性能要件となります。センサーからの信号は非常に微弱であり、外来ノイズや電源由来のリップルが混入すると正確な信号処理が困難になります。したがって、低ノイズ設計だけでなく、アナログフロントエンド回路や電源回路全体を通じた高SNRの確保が求められます。また、変動の少ない電源供給はAD変換精度にも影響するため、アナログASICにおける電源設計は非常に重要な要素です。

センサー特性に合わせた回路ブロック構成と設計手法

センサー向けアナログASICでは、ターゲットとするセンサーの物理特性(例:抵抗変化、容量変化、電荷出力など)に応じて、アンプ構成やフィルタ、AD変換器などの回路ブロックを柔軟に構成する必要があります。たとえば、フォトダイオードを扱う場合は低暗電流アンプが、圧力センサーではブリッジアンプや可変ゲインアンプが有効です。各ブロックはセンサーの感度帯域に最適化され、かつ電源や基板条件を含めた全体最適が求められます。これによりノイズ・線形性・応答性をバランス良く確保する設計が可能となります。

アナログASICに最適なLDOレギュレーターとは

アナログ信号処理において、電源の質は回路全体の性能を左右する決定的な要素です。特にセンサー応用では、電源由来のノイズや変動がそのまま出力信号の精度に影響するため、LDOレギュレーターの品質が非常に重要です。LDOはリニアレギュレーターの一種で、電圧の安定供給とノイズ除去に優れた特性を持ちます。アナログASICと組み合わせて使用することで、センサーフロントエンドの信号処理精度を飛躍的に高めることが可能です。特に、内部にLDOを組み込むことで、外部ノイズの遮断や複数電圧系統の統合制御がしやすくなり、システム全体の安定性と設計自由度が向上します。

LDOレギュレーターの基礎とアナログASIC設計における位置付け

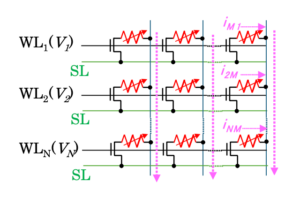

LDO(Low Dropout)レギュレーターは、入力と出力間の電圧差が小さくても安定して電圧を供給できるリニア電源ICです。アナログASICでは、高精度な電源供給が求められるため、LDOは極めて重要な役割を担います。特にセンサーフロントエンド回路において、電源由来のノイズを抑えるためにLDOが使われるケースが多く、高PSRR(電源電圧変動除去比)や低ノイズ性能が必須です。また、ASIC内部にLDOを組み込むことで、外部ノイズからのアイソレーションや、複数電圧ドメインの分離にも活用できます。

低ノイズ・高PSRR・高速応答がもたらす設計上のメリット

LDOにおける低ノイズ設計は、アナログ信号処理の精度を確保するために不可欠です。高PSRR性能により、入力電源の変動やスイッチングノイズの影響を大きく抑制でき、センサー出力の信号品質を損なわずに処理が可能になります。また、近年のセンサー応用では、モード切替や周期駆動が一般的であり、それに伴う負荷変動に即応できる高速トランジェント応答も求められます。これらの特性を備えたLDOは、設計の自由度を高め、フロントエンドからADCまでの一貫した高精度信号処理を実現します。

LDO選定・設計時に留意すべき電源制約と安定動作条件

LDOの導入にあたっては、ASICの動作電圧・消費電流・発熱設計といった電源制約を十分に考慮する必要があります。たとえば、LDOはドロップアウト電圧分の電力を熱として消費するため、電源マージンが少ない設計では熱設計や放熱構造が重要になります。また、負荷変動時に発振や不安定動作が起こらないよう、適切な補償設計や外部コンデンサの選定も必要です。高PSRRを維持しつつ、負荷や温度変化に対して安定した動作を確保するためには、回路定数のチューニングとシミュレーションの積み重ねが重要です。

実装設計におけるLDOとアナログブロックの統合戦略

LDOレギュレーターをアナログASIC内に統合することで、電源品質とレイアウト最適化を同時に実現できます。ただし、その設計には慎重な検討が必要です。ノイズ源からの物理的距離やグラウンドプレーンの分離など、レイアウト段階での設計判断が性能に大きく影響します。また、LDOの出力が不安定になると、センサー信号処理に支障をきたすため、デカップリングや応答試験といった検証も重要です。このセクションでは、LDOとアナログブロックを物理的・機能的に最適配置するための手法と、実装上の注意点を紹介します。安定した信号処理と電源制御を両立するための戦略設計が求められます。

レイアウトにおけるノイズ源管理とLDO配置のベストプラクティス

アナログASICにおけるLDOレギュレーターの物理的配置は、ノイズ対策の観点で極めて重要です。レイアウト段階では、LDOの出力ラインをアナログブロックにできる限り近づけ、電圧供給経路を短く保つことで電源インピーダンスの低減とノイズ混入の抑制が可能になります。また、デジタル領域やクロックラインといった高周波ノイズ源から距離を取ること、GNDプレーンを分離することも有効な対策です。LDO自体のバイパスコンデンサ配置や帰還経路設計も安定性と雑音耐性に直結するため、慎重な設計が求められます。

ASIC内部でのLDO出力安定化とデカップリング設計

LDO出力の安定化には、適切なデカップリングコンデンサの配置が不可欠です。センサー信号処理回路は瞬時の電流変動に対して敏感であり、電源電圧が一時的にドロップすると計測精度や動作安定性が著しく低下する恐れがあります。そのため、LDO直後に高速応答型の小容量コンデンサを配置し、負荷の近傍には大容量のバルクコンデンサを併設することで広帯域な安定化が実現されます。また、パッケージ内インダクタンスや配線長も考慮し、シミュレーションを用いて共振やリンギングが起きないよう設計する必要があります。

トランジェント応答試験と評価項目の設計段階での想定

LDOのトランジェント応答性能は、負荷電流が急変するセンサー制御回路において特に重要です。設計段階では、動作モード遷移時に生じる突発的な負荷変動に対して、出力電圧が規定内に収まることを確認する必要があります。このため、設計初期からトランジェント試験条件(立上り時間、電流ステップ幅、観測時間窓など)を明確化し、応答波形の解析や電圧リップルの最大値評価を行うことが推奨されます。トランジェント特性はループ補償設計や出力コンデンサ構成に強く依存するため、各要素のチューニングが製品安定性を大きく左右します。

まとめ

センサー向けアナログASICの性能を最大限に発揮させるには、LDOレギュレーターを含む電源設計の最適化が不可欠です。本記事では、LDOの基本機能から、ノイズ・PSRR・応答特性といった詳細な設計ポイント、さらには実装上のベストプラクティスに至るまでを解説しました。今後のセンサー技術の進化とともに、電源設計はさらに複雑化することが予想されますが、アナログASICとLDOの融合により、システム全体の安定性と信号品質を高次元で実現することが可能です。設計エンジニアは、LDOの役割を単なる電圧供給ではなく、システム性能を決定づける要素として位置付ける視点が求められます。

センサー用アナログASICにおけるLDOの設計的意義

センサー応用に特化したアナログASICでは、LDOレギュレーターは単なる電源供給回路ではなく、信号品質を支える中核的な構成要素です。特にノイズ除去性能や電源変動への耐性が、センサー全体の性能を左右します。アナログ回路における微細な信号の忠実な処理には、高性能なLDOを通じて安定した電源環境を整備することが極めて重要です。また、ASIC内部に統合することでレイアウト自由度も向上し、全体設計の最適化に寄与します。LDO設計はアナログASIC開発における不可欠な専門領域と言えるでしょう。

性能最適化のためのLDO設計・評価ポイント

LDOレギュレーターの性能を最大限に引き出すには、設計と評価を一体化したアプローチが重要です。具体的には、PSRRや出力ノイズだけでなく、トランジェント応答特性、負荷安定性、温度ドリフト、静止電流など、複数の観点での評価が求められます。評価条件も実際のセンサー動作条件に近い形で設定することで、実使用時の挙動を正確に捉えることができます。また、回路設計段階でのSPICEシミュレーションや、レイアウト後の寄生素子を考慮した検証も不可欠です。これにより、シリコン実装後のトラブルを最小限に抑えることが可能になります。

次世代センサー応用に向けたアナログASIC設計トレンド

近年のセンサー応用では、より高精度・高速・低消費電力を同時に求める傾向が強まっています。これに伴い、アナログASIC設計でもマルチチャネル対応やデジタル補正機構の内蔵、さらにはLDOの複数インスタンス化による局所電源供給などが一般的になりつつあります。また、プロセス微細化によりLDOの設計自由度が高まる一方で、レギュレーター性能の確保にはトレードオフも存在します。今後は、アナログ性能と電源安定性の両立を目指し、より精緻な設計手法と評価フレームワークが求められることになるでしょう。

FeRAM搭載アナログASICの設計・開発サービスについて

https://www.ramxeed.com/jp/products/asic-assp/