認証デバイス向けアナログASICの設計と技術的考察

認証デバイスにおけるアナログASICの役割や設計技術について解説します。信号精度の確保、省電力性、PUF活用など最新のセキュリティ要求に対応するための要点を詳しく紹介しています。

認証デバイスにおけるアナログASICの役割

認証デバイスにおいて、アナログASICはセンサからの信号を正確かつ安定して処理するための中核的な要素です。生体認証や物理トークン認証といった用途では、指紋、静脈、電圧変化などのアナログ信号を高精度に取得し、後段のデジタル認証処理へと橋渡しする必要があります。汎用ICの組み合わせでは達成が難しい低ノイズ性や省電力性を、アプリケーション特化型のアナログASICにより実現できます。高集積設計によって小型化と高信頼性を両立し、エッジ用途でも高いセキュリティレベルを保持可能です。

認証デバイスの代表例とシステム構成

認証デバイスには、生体認証機器、アクセス制御システム、IoT向けセキュリティモジュールなど多様な応用例があります。いずれも高精度な入力信号処理と不正検出を行う必要があり、そのためにセンサ、アンプ、フィルタ、A/D変換回路、認証ロジックなどが統合されたシステム構成を持ちます。中でも、アナログ信号を扱うフロントエンド部分は、システム全体の認証精度や応答性を左右する要であり、ここにアナログASICの専用設計技術が活用されます。

アナログASICが担う主要な回路機能

アナログASICは、信号処理の起点となる増幅回路やフィルタリング回路、A/D変換回路、さらには温度補償やリファレンス電源回路など、多様な機能を集積することが可能です。これらの回路は、外部センサからの微小信号を安定して扱うために最適化されており、システムの感度やセキュリティ精度を大きく左右します。また、製品固有の動作特性を付加することで、認証の個体識別機能やトラストアンカーとしての役割も果たします。こうした集積回路によって、設計全体の高性能化と差別化が実現されます。

ディスクリート構成との比較と統合のメリット

ディスクリート構成では、複数のアナログICや受動部品を組み合わせて信号処理を実現しますが、ボード設計の複雑化、ノイズ源の増加、トリミング工数などが設計負荷として現れます。対して、アナログASICは必要な回路を1チップに集約することで、回路間のマッチング精度を高め、面積・消費電力の両面で最適化された設計が可能になります。さらに、特定の用途に特化した設計により、部品点数削減や信頼性向上が図れ、製造コストや品質管理の観点でも有利に働きます。

アナログASIC設計のプロセスと技術的要点

アナログASICの設計プロセスは、用途ごとに最適な特性を達成するための仕様定義から始まり、トポロジー選定、回路設計、レイアウト、検証を経て製造へと至ります。特に認証用途では、信号の整合性と再現性、環境耐性、製品ごとの差異の最小化が重要です。一般的なIP再利用が困難なケースも多く、回路構成は個別に設計されることが多いです。ここでは、トランジスタレベルでの回路設計と物理レイアウトの密接な連携が要求され、経験に裏打ちされた設計判断が不可欠です。

設計仕様の策定と要素技術の選定

設計仕様は、対象とする認証デバイスの要求精度、動作電圧、温度範囲、帯域、ノイズ許容度などを明確に定義するところから始まります。その上で、必要な回路ブロック(アンプ、ADC、基準電圧、電源管理等)を洗い出し、それぞれの性能要件に基づいたアーキテクチャを選定します。特にセキュリティ用途では、電源変動や温度変化に対しても一貫した性能を示す回路が求められるため、ばらつき制御技術やオフセットキャンセル技術の導入が重要です。

レイアウト設計におけるノイズと干渉対策

レイアウト設計では、クロストークや寄生要素、電源リップルなどによる性能劣化を防ぐためのノイズ抑制技術が不可欠です。アナログ回路はデジタルに比べて感度が高く、GNDのインピーダンスや配線の長さ、対向面積といった物理構造が動作に影響を与えるため、慎重なフロアプランが求められます。また、セキュリティ用途では物理攻撃耐性の観点から、レイアウトレベルでの情報漏洩対策(例:差動信号化やサイドチャネル耐性設計)も重要な設計要素となります。

検証段階での課題と測定技術の活用

設計完了後はシミュレーションとシリコン評価による動作確認が行われますが、アナログ回路は動作点が環境やロットごとに変化しやすく、理論通りの結果が得られないことも少なくありません。このため、検証段階ではコーナーシミュレーションやMonte Carlo解析、さらには実機を用いた温度・電圧変動テストが重要となります。測定には高精度なプロービング技術や自動化測定システムが活用され、開発期間の短縮と設計フィードバックの精度向上が図られます。

アナログ信号を用いたハードウェア認証技術

ハードウェアベースの認証技術では、アナログ信号の個体差や自然界のノイズを利用した物理的識別手法が注目されています。これらの技術は、従来のデジタル認証に比べてクローン耐性が高く、PUF(Physically Unclonable Function)やアナログスクランブル手法などが実用化されています。アナログASICは、これらの機能を高精度かつ省電力で統合するための理想的なプラットフォームです。センサ信号を基盤とした認証では、ノイズと信号の分離性能が重要となり、アナログ設計の高度な知見が必要です。

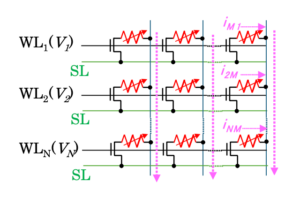

PUFによる設計と応用

PUFは、シリコン上のばらつきや回路特性の自然な差異を用いて、一意の識別情報を生成する仕組みです。この技術はデバイス固有のフィンガープリントとして利用され、秘密鍵の格納を必要としない高セキュリティな認証方式を実現します。アナログASICでは、回路ばらつきを意図的に設計に組み込み、安定したPUF応答を得るためのバイアス制御や補正技術が重要です。PUFはトークン認証、IoTデバイスのセキュア起動、改ざん検出など、広範な応用が可能です。

アナログスクランブル信号による改ざん防止手法

アナログスクランブルとは、センサ出力信号に対して特定の変調やランダマイズ処理を加えることで、外部からの不正読み取りや改ざんを困難にする手法です。この手法では、入力信号が再現不可能なランダム性を持ち、予測困難な応答を生み出すため、高度なセキュリティが実現されます。アナログASICはこの処理をリアルタイムで実装でき、認証精度を損なうことなくセキュリティを強化します。設計には変調回路、乱数生成器、復号ロジックなどが密接に関わります。

センサ応答の個体差を利用した識別技術

センサデバイスは製造上のばらつきや素材特性により、同一品番でも微妙に異なる応答特性を持ちます。これらの差異は本来、ばらつきとして扱われますが、逆に認証用途では識別情報として利用することが可能です。特定周波数での応答特性、温度変化時の電圧応答、静電容量の変動といった特徴を用いて、個体認証や真正性検証を行う設計が進んでいます。アナログASICはこうした個体差を検出・処理するための最適な構成要素を提供します。

セキュリティ対応設計に向けた将来展望

アナログASICは、セキュリティ技術の進化に伴い、その設計要件も高度化・多様化しています。特に、IoTやエッジコンピューティング領域における認証機能では、電力効率とリアルタイム処理能力、そして外部攻撃に対する耐性が同時に求められます。アナログASICは、これら複雑な要件に対して、高い設計自由度と回路最適化を提供できる手段として今後も重要性を増していくと考えられます。柔軟なカスタム設計と量産性の両立が、将来の製品競争力の鍵となるでしょう。

低消費電力と高セキュリティの両立設計

セキュリティ機能は通常、常時動作や連続監視を必要とするため、消費電力の増加が設計課題となります。特にバッテリー駆動のエッジデバイスやウェアラブル機器においては、ミリワット以下での動作を実現しつつ、強固な認証プロセスを維持することが求められます。アナログASICでは、専用の電源制御回路や省電力アーキテクチャを導入することで、これらの要件に対応可能です。セキュアスタンバイモードやオンデマンド認証機能を備えた設計が今後の主流になると考えられます。

多様な認証方式に対応する回路柔軟性

近年は、生体認証、暗号トークン、PUF、物理トラストベースなど、さまざまな認証方式が混在しており、ひとつの認証手法だけでなく複数方式の併用が進んでいます。このような中で、アナログASICには高い構成柔軟性と拡張性が求められます。例えば、センサ入力の種別変更やフィルタ帯域調整、出力フォーマットの可変化など、設計段階で複数の仕様に対応できるアーキテクチャが求められています。柔軟なマルチモーダル対応こそ、次世代認証機器の設計力の差となります。

アナログ設計の継承と技術者育成課題

アナログASIC設計は高度なアナログ回路理論と実践的なレイアウト技術を要する分野であり、長年の経験に支えられた属人的な要素が多いという課題があります。近年、若手エンジニアの育成が難しくなっており、設計ノウハウの継承や標準化、設計支援ツールの高度化が急務です。また、モデルベース設計やAIによるレイアウト支援技術の活用が始まっており、これらを導入することで属人性を低減し、再現性の高い設計フローを確立することが、今後の競争力につながります。

まとめ

アナログASICは、認証デバイスの高性能化と小型化、省電力化を同時に実現するために極めて重要な要素です。特にセキュリティ分野においては、回路レベルでの防御力や信号の一貫性がシステム全体の安全性を左右します。本記事では、アナログASICが認証技術において果たす役割とその設計要点、さらには将来に向けた技術的展望について解説しました。今後、設計者は多様な認証技術への対応力を高め、よりスマートで堅牢なアナログ設計を志向することが求められます。

認証デバイスにおけるアナログASICの設計意義

認証デバイスにおいて、アナログASICはセキュリティの要となる信号処理を物理レイヤーで担う重要な存在です。センサからの微小信号の取得や外乱除去、個体識別のための特性抽出など、多様な処理を低消費電力かつ高精度で実現します。さらに、信頼性の高い一体型設計によってデバイスの小型化と高集積化が可能となり、携帯端末やエッジノードへの応用範囲も広がります。アナログASICを適切に設計・活用することが、認証機器全体の競争力向上につながります。

技術的要点と設計現場での実装ポイント

アナログASICを設計する際には、仕様の明確化、回路ブロックの最適選定、ノイズ対策、レイアウト戦略、実機検証といった要素を段階的かつ整合的に進める必要があります。また、認証用途ではセキュリティ機能のための耐タンパ性やPUF応答の安定性など、設計初期から考慮すべき要素が追加されます。実装においては、再現性のある動作特性の確保と、製造ばらつきへの対応力が重要となります。これらを踏まえた体系的な設計が成功の鍵です。

将来のセキュリティ需要に対応する設計力とは

今後、IoTやモバイル、産業機器などさまざまな分野で認証機能が求められるようになる中、アナログASICにはより高度で柔軟な設計が要求されます。設計者は、単なる回路動作の最適化だけでなく、セキュリティレベルや運用環境まで見据えた包括的な設計視点が必要です。PUFやアナログスクランブルなど新技術の理解と導入、そして設計ツール・人材の活用による効率的な開発体制構築が、今後の認証デバイス設計の差別化要因となるでしょう。

FeRAM搭載アナログASICの設計・開発サービスについて

https://www.ramxeed.com/jp/products/asic-assp/