アナログASICにおけるA/Dコンバータ統合設計の実践と基礎知識

アナログASICにおけるA/Dコンバータ統合設計の基礎から応用までを解説し、方式選定や設計戦略、最新事例とツール活用法を紹介します。性能・消費電力・信頼性を高めるための実践的な知識を提供します。

アナログASICにおけるA/Dコンバータの基礎と役割

アナログASICに統合されるA/Dコンバータ(ADC)は、アナログ信号をデジタルに変換する重要な機能を担い、性能・消費電力・チップ面積の最適化が求められます。特にミックスドシグナル設計では、信号整合性やノイズ耐性、タイミング精度の確保が必須であり、プリアンプやフィルタ、リファレンス回路といった周辺回路との統合設計が不可欠です。また、温度特性や長期安定性の管理も高信頼性システムでは欠かせません。適切なアーキテクチャ選定と電源分離設計を行うことで、システム全体の効率と信頼性を向上させることができます。

A/Dコンバータの基本原理:標本化・量子化・符号化

A/Dコンバータは、標本化・量子化・符号化の三工程でアナログ信号をデジタルに変換します。標本化では入力信号を一定周期でサンプリングし、量子化で各サンプル値を最も近いレベルに丸めます。符号化では量子化結果をデジタル形式に変換します。性能はサンプリング周波数と分解能のバランスに依存し、アンチエイリアシングフィルタ設計が不可欠です。さらに同期回路や基準電圧源の安定度、入力段のノイズ特性も全体性能を左右するため、包括的な設計が重要です。

解像度・サンプリング速度・ENOBとは?

ADCの解像度はビット数で表され、12ビットなら4096段階を識別可能です。サンプリング速度は1秒間の標本化回数で、信号帯域幅に直結します。ENOB(実効ビット数)はノイズや歪みの影響を反映した実用的な分解能で、理論値との差は設計や環境に起因します。これら三要素は相互に影響し合い、用途や信号特性に応じたバランス設計が必要です。高精度計測ではENOBの向上が重要であり、高速通信ではサンプリング速度を優先するなど、目的に応じた最適化が求められます。

用途別のA/Dコンバータ方式(SAR/ΔΣ/パイプライン)

SAR型ADCは低消費電力で中速・中精度を両立し、センサやモバイル用途に適します。ΔΣ型は高分解能だが低速で、音響や計測向けです。パイプライン型は高速変換が可能で、通信やRFシステムに向きます。方式ごとにクロック構成やフィルタ条件、消費電力特性が異なり、単純な精度や速度比較だけでは最適化できません。近年はハイブリッドADCも登場し、異なるアーキテクチャの利点を組み合わせた設計が可能になっており、用途特化型の開発が進んでいます。

アナログASICに統合されたA/Dコンバータの設計戦略

アナログASICにADCを統合する際は、システム設計から回路、レイアウト、検証までを一貫して最適化する必要があります。アナログとデジタルの干渉を抑えるフロアプラン設計や電源分離は基本です。CMOSは低消費電力で汎用性が高く、BiCMOSは広帯域性能に優れています。統合化に伴うノイズや寄生容量の影響は複雑化するため、EDAツールを駆使して早期検知し対策します。さらに試作評価によるフィードバックを迅速に反映できる開発プロセスが信頼性向上に直結します。

混載(Mixed-Signal)ASICの設計フロー

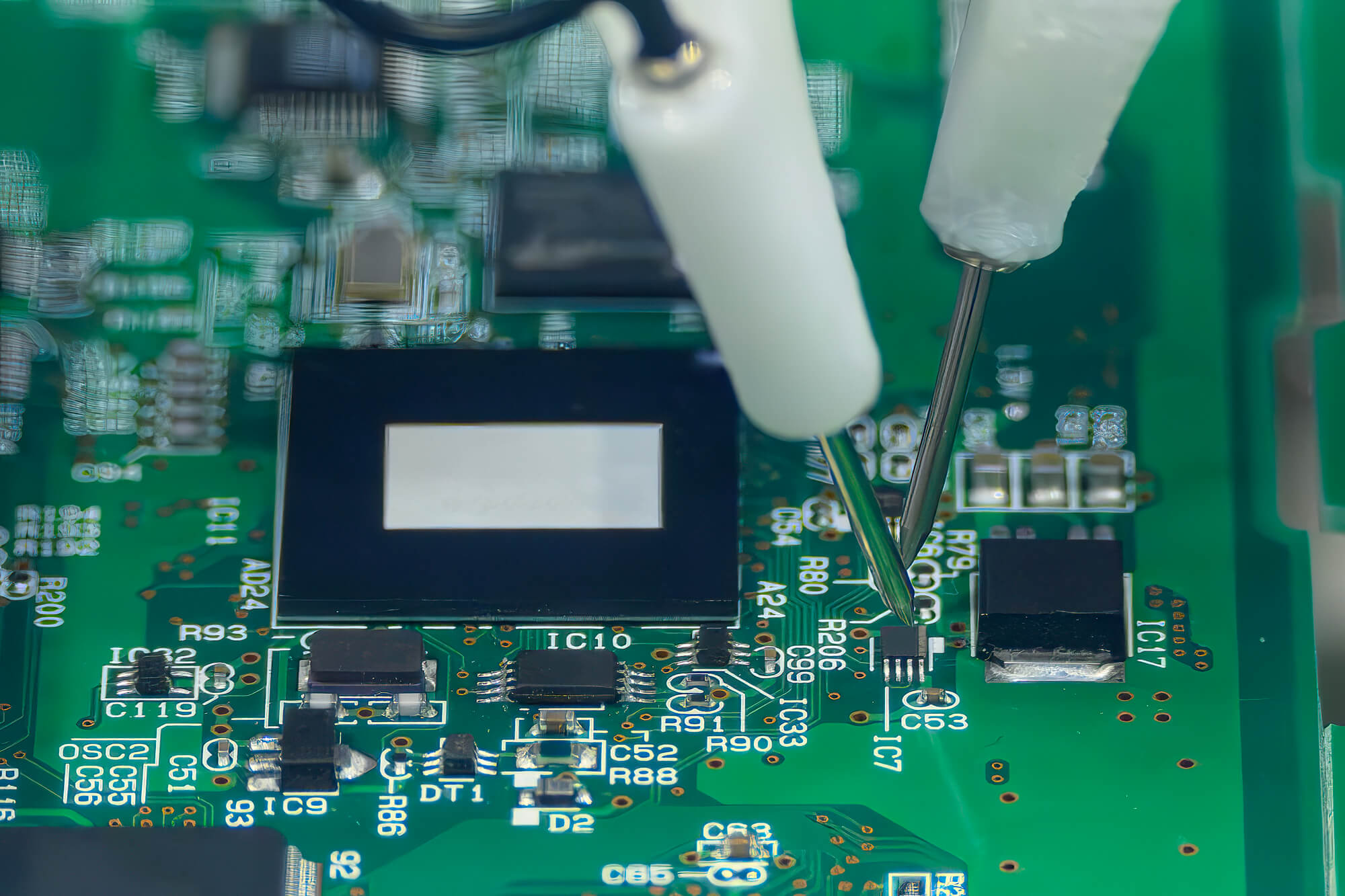

Mixed-Signal ASICの設計は、システム要件定義から始まり、ADC構成やインタフェース仕様を策定します。アナログとデジタルの設計は並行し、それぞれ独立シミュレーション後に統合検証を実施します。フロアプランでは物理的分離やガードリング配置で干渉を抑制します。DRC、LVS、PEXなどの物理検証を経て製造データを生成します。設計初期から論理と物理の整合性を意識し、進捗管理やリスク評価も同時進行で行うことが成功の鍵です。

CMOS/BiCMOS技術とアナログセクション設計手法

CMOSは低消費電力と高集積度を特長とし、ADC統合に広く利用されます。BiCMOSは高周波特性と省電力性を兼ね備え、広帯域・高精度用途に適します。設計ではトランジスタのマッチング、レイアウト対称性、電源・基板ノイズ対策が必須です。CMOSではスイッチングノイズ低減策、BiCMOSではコストや設計制約対応が課題となります。早期の技術選定と最適モデル活用が成功を左右し、量産時のばらつき管理や品質保証体制の構築も不可欠です。

設計上の主な課題(ノイズ、非線形性、寄生容量など)

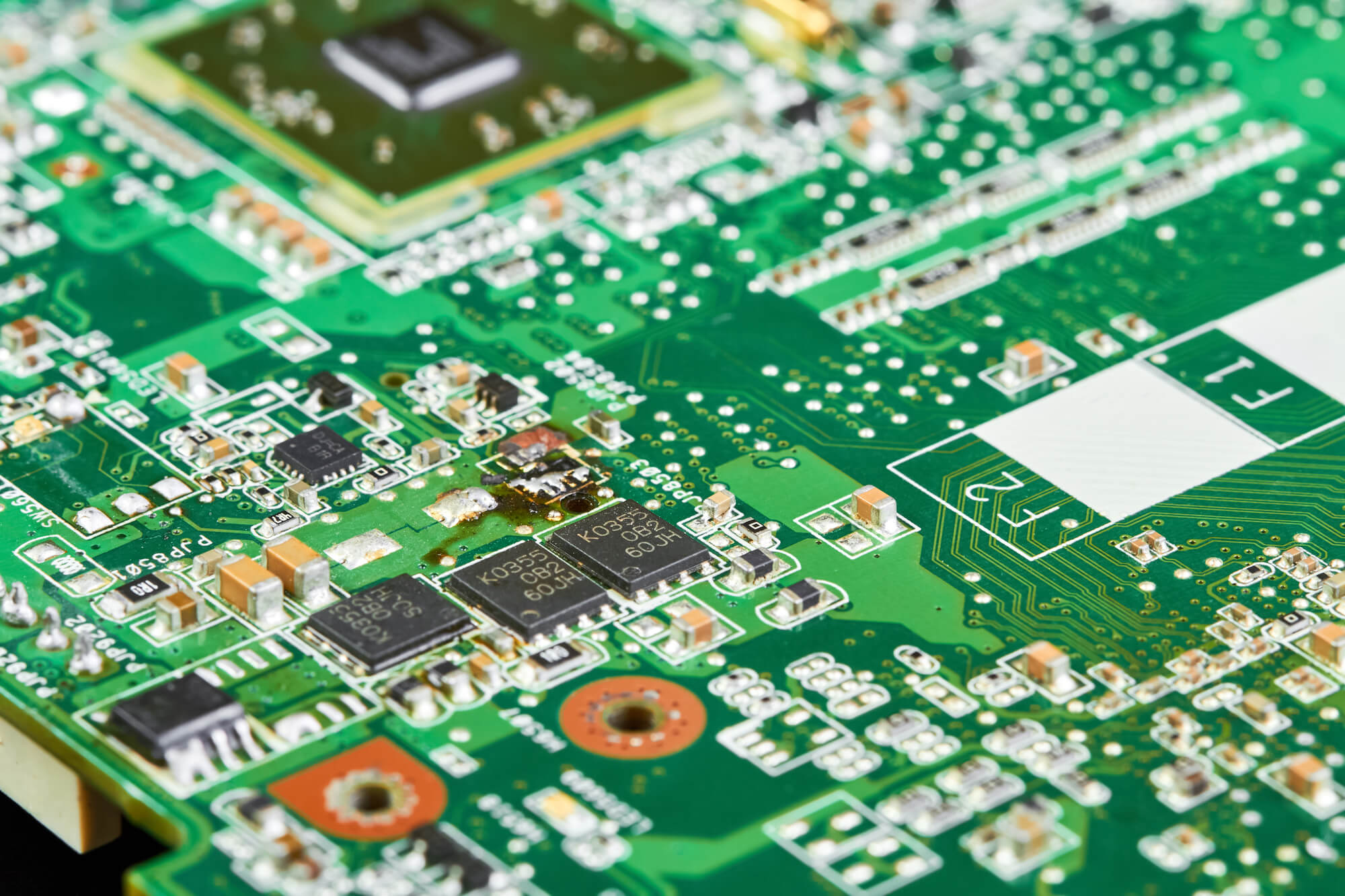

ADC設計における主要課題は、熱雑音やスイッチングノイズなどのノイズ、INLやDNLで評価される非線形性、そして寄生容量です。これらは回路構成やレイアウト、フロアプランに影響します。ミックスドシグナル環境ではクロストークも問題となり、EMC対策やアナログ・デジタルの物理的分離が有効です。事前シミュレーションで問題を洗い出し、補正やキャリブレーション回路を導入することで性能低下を防ぎます。長期信頼性確保には温度や経年変化への耐性設計も必要です。

まとめ

設計エンジニアにとってのポイント整理

ADC統合設計では、アーキテクチャ選定からノイズ対策、レイアウト分離、電源安定化まで多面的な配慮が必要です。用途ごとに速度・分解能・消費電力の優先度を整理し、設計初期から全体最適を図ることが性能と信頼性向上に直結します。EDAツールやシミュレーションの活用により、課題の早期発見と改善が可能となります。さらに製造・評価フェーズでのフィードバックを設計へ反映する継続的改善が、競争力ある製品づくりの基盤となります。

最新ツール・ライブラリの活用と将来展望

近年のEDAツールは、回路設計からレイアウト、物理検証までを統合的に支援し、混載ASICの開発効率を大幅に高めています。オープンソースの回路ライブラリや自動配置配線ツールの精度向上により、低コストかつ高品質な設計が可能になりました。将来的にはAIを活用した自動補正や最適化が一般化し、複雑なADC統合設計も短期間で実現可能になると予想されます。これにより、より高度で省電力な製品開発が加速するでしょう。

不揮発性メモリ設計への応用機会と相性

ADC技術は、不揮発性メモリ(NVM)を活用したシステムにも応用可能です。特にセンサデータを長期間蓄積しつつ低消費電力で動作するエッジデバイスでは、ADCとNVMの組み合わせが有効です。例えばFeRAM搭載ASICは、高速書き込みと低消費電力特性により、連続計測やイベント検出用途で有利です。ADC出力を直接NVMに格納する設計により、データロス低減とシステム簡素化が実現できます。今後はIoTや車載分野での採用がさらに拡大する見込みです。

FeRAM搭載アナログASICの設計・開発サービスについて

https://www.ramxeed.com/jp/products/asic-assp/