アナログASICで実現するRFIDセンサータグの概要と設計ポイント

RFIDセンサータグにおけるアナログASICの活用について、基本構成や設計の技術ポイントを解説します。低消費電力や高集積化、信号処理精度の向上を実現する設計手法を紹介します。

RFIDセンサータグの基本構成と技術要件

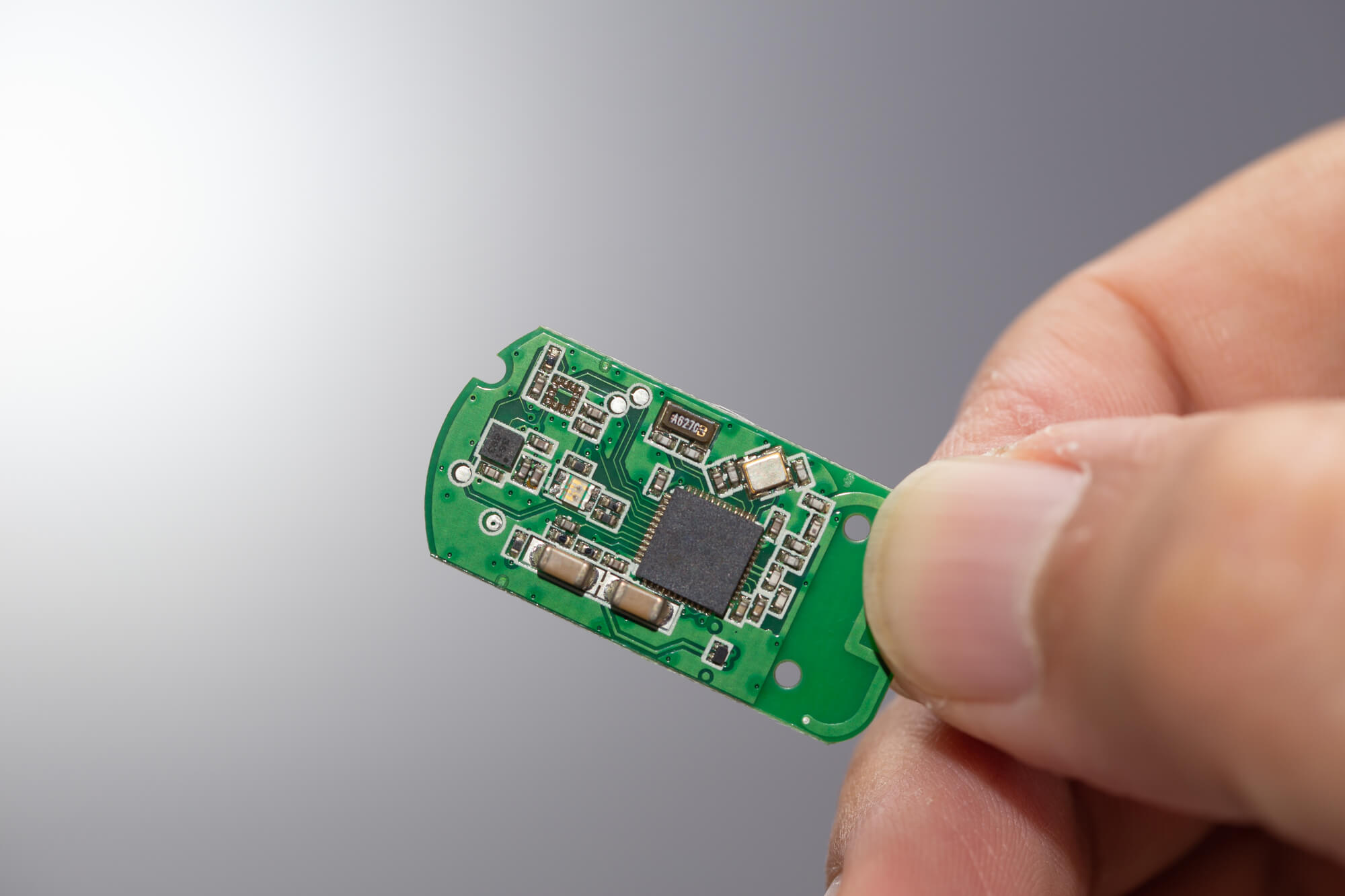

RFIDセンサータグは、無線による非接触通信とセンサーによる物理量の検出を統合したデバイスであり、電源供給をリーダからの電波に依存するという特性があります。このため、限られたエネルギーで確実に動作する高効率な回路設計が求められます。アンテナ、整流回路、センサー、信号処理、ADC、制御ロジック、通信モジュールなどがコンパクトに集積され、それぞれが低消費かつ協調的に機能する必要があります。

RFIDセンサータグのブロック構成と動作概要

RFIDセンサータグは、外部のリーダから送信されるRF信号をアンテナで受信し、整流回路によって直流電源へ変換するところから動作が始まります。得られた電力を用いて内部回路を起動し、センサーで取得したアナログ信号を処理してデジタルデータに変換し、タグが通信プロトコルに従ってそのデータをリーダへ返信します。タグ内部では整流回路、バンドギャップ電源、センサーインタフェース、AD変換器、メモリ、変調器などの各機能が連携して動作します。これらが限られた電力と極小の面積で機能するよう、厳密な回路設計とシステム構成が必要になります。

センサー信号の取得と処理に必要な要件

RFIDタグ内で扱われるセンサー信号は一般に数mV〜数百mVの微小なアナログ量であり、その精度と信号対雑音比(S/N比)を維持したままADCへ入力することが要求されます。そのため、前段に設けるアナログ処理回路には、低ノイズアンプ、バンドパスフィルタ、チョッパ安定化回路などの構成が必要となる場合があります。また、センサーの種類に応じて入力インピーダンスやオフセット特性が異なるため、汎用回路では対応しきれない微調整が求められるケースも多く、これらをチップレベルで最適化できるのがアナログASICの大きな利点です。

タグに求められる消費電力・応答性・集積性の指標

RFIDセンサータグの運用では、起動電圧の低さと待機電流の少なさが動作信頼性を大きく左右します。例えば、パッシブ型タグでは数百μW以下の消費電力で安定動作させる必要があり、アナログおよびデジタル回路のスリープ制御やクロックゲーティングが鍵となります。また、リーダの通信プロトコルに対してタイムリーに応答できるよう、信号処理からデータ送信までのレイテンシを最小化する設計が不可欠です。さらに、タグの物理的寸法が制約される場合が多く、全機能を1チップに統合する高集積設計が求められます。

アナログASICが汎用ICに勝る理由と適用領域

RFIDセンサータグのように電力、面積、機能のすべてに制約がかかる用途では、汎用ICの組み合わせでは限界が生じる場面が多くあります。アナログASICは、これらの制約を回避しつつ、アプリケーションごとに最適な回路構成を実現できる手段として非常に有効です。ここでは低消費電力性、信号精度、機能一体化といった観点から、アナログASICの実装上の優位性を掘り下げていきます。

超低消費電力を実現する回路最適化の自由度

アナログASICは、動作電流やスイッチングタイミングをチップ設計レベルから制御可能であるため、消費電力の最小化を徹底できます。例えば、センサーを周期的に動作させる際に、センサーブロック全体をタイミング的に遮断する機構や、電源バイアスの段階的供給を行う設計など、用途に応じたパワーゲーティングが容易に実装できます。また、不要な機能を排除し、電圧レベルを最小限に設定することで、数μWレベルの動作も現実的になります。こうした設計自由度は、汎用ICでは実現が難しい領域です。

ノイズ耐性・信号精度を向上させるカスタム設計

センサー信号は極めて微弱であり、外部ノイズやオフセットドリフトの影響を受けやすいため、アナログ信号処理の精度がデータの信頼性を左右します。アナログASICでは、センサー近傍に増幅器やフィルタを物理的に配置できるため、配線経路の短縮によってノイズの混入を抑制できます。また、レイアウト設計においても対称性やガードリングを意識したパターン設計が可能となり、外乱に対する堅牢性が向上します。さらに、温度補償やオフセット補正機能を回路内に組み込むことで、精度面でも高い安定性を確保できます。

センサー・通信・電源制御の一体最適化による設計効率

アナログASICを採用することで、センサー入力からデータ処理、通信出力に至るまでの信号処理フロー全体をチップレベルで一体化できます。これにより、外部とのインタフェース回路が削減され、遅延要因やバス競合のリスクを回避できます。たとえば、ADCと変調器を同一クロックドメインで同期させることで、応答遅延を抑えることが可能です。また、RF給電の安定性を見ながら回路の部分動作を制御するパワーマネジメントも組み込めるため、タグ全体の動作効率が格段に向上します。

アナログASICによるRFIDタグ設計の技術ポイント

アナログASICを実際にRFIDタグへ適用する際には、設計思想を回路構成にどう落とし込むかが重要です。特にセンサー信号の処理、給電環境に適応した電源回路、データ保存のためのメモリ制御など、複数の技術領域が密接に関係します。ここではそれぞれの設計要素における注意点と、アナログASICならではの実装上の工夫について具体的に解説します。

センサーインタフェースとADC前段の設計注意点

センサー信号は一般的にアナログ量で出力されるため、AD変換前のインタフェース回路は非常に重要です。アナログASICでは、センサー特性に応じた入力インピーダンス設計、低オフセット増幅器の選定、フィルタ設計が可能であり、信号の忠実な取得を支援します。センサー出力が微弱な場合、ノイズリダクションのためのチョッパ安定化技術や、差動構成によるコモンモード除去設計も導入可能です。さらに、センサーの複数入力対応にはアナログマルチプレクサを用いた柔軟な構成も取ることができます。

電源整流回路・起動電圧制御の最適化手法

パッシブ型RFIDタグにおいては、電源供給が完全にリーダからのRF信号に依存しており、低電圧での起動性能が全体の信頼性を左右します。アナログASICでは、整流回路においてトランジスタ構成を工夫し、しきい値電圧の低減や電流駆動能力の向上が可能です。また、レギュレータ回路とバンドギャップ参照電源を一体化することで、低負荷条件下でも安定した電圧供給を実現できます。加えて、パワーオンリセット回路やスリープモードの動作制御回路を集積することで、電源が不安定な状態でも確実なシステム起動が行えます。

信号処理とメモリ制御の集積設計による利点

RFIDタグには、センサーで得られたデータを一時保存するためのメモリが搭載されますが、これを制御するための回路がタグ全体の効率に大きく影響します。アナログASICでは、ADC出力を直接メモリ制御部に接続し、バスを介さずに高速かつ低消費電力でデータ格納を行う構成が可能です。また、センサーごとのキャリブレーション値や温度補正パラメータを保持する不揮発性メモリも同一チップ上に実装することで、外部回路なしで高精度な補正処理が行えます。さらに、書き込み回数の最適化やパルス制御によるピーク電流削減など、きめ細かい制御も実現可能です。

まとめ

RFIDセンサータグの設計において、アナログASICは極めて有効な選択肢です。消費電力、精度、面積、応答性といった厳しい設計制約をクリアしつつ、タグの性能を最大化するためには、用途に最適化されたアナログ回路の導入が鍵となります。以下に、これまでの論点を整理し、今後の展望を交えた設計観点をまとめます。

アナログASIC設計の本質的メリットの総括

アナログASICの最大の価値は、用途特化による最適化設計が可能な点にあります。RFIDタグは厳しい電力制約と高い通信性能を両立しなければならず、一般的なICでは不要な機能がオーバーヘッドとなりやすい状況です。ASICでは、必要な機能だけを厳選し、プロセスやレイアウトもアプリケーションに最適化できるため、動作効率、応答性、ノイズ特性すべてにおいて高い水準を実現できます。これにより、低消費電力・高精度なセンサータグの構築が可能となります。

RFIDセンサータグ設計に求められる視点の再整理

RFIDセンサータグの設計では、単に各ブロックを高性能にするだけでは不十分であり、全体の連携を重視したシステムレベルの設計が重要です。たとえば、センサーの動作タイミングと通信シーケンスの整合性、電力供給の変動に対する応答戦略、温度ドリフトを抑える補正処理など、設計者には複合的な視点が求められます。これらをチップレベルで制御・統合できるアナログASICは、複雑な要件を満たすための最適な実装手段として機能します。

今後の技術動向と設計上の考慮ポイント

RFIDセンサータグの応用領域は、物流トラッキング、医療機器、食品モニタリング、構造物監視など多様化が進んでおり、用途ごとに異なる要求仕様が出てきています。これに伴い、設計者はより柔軟かつ高効率な設計アプローチを求められるようになります。今後は、フレキシブル基板や印刷技術との融合、マルチセンサ統合、エネルギーハーベストの高効率化といった要素が重要になるでしょう。こうした変化に適応するには、アナログASICによる高度な回路統合とシステム最適化が設計の中核となることは間違いありません。

FeRAM搭載アナログASICの設計・開発サービスについて

https://www.ramxeed.com/jp/products/asic-assp/

FeRAM搭載RFIDを選ぶ理由

https://www.ramxeed.com/jp/products/asic-assp/why-feram-rfids/

プレスリリース:FeRAM搭載ASSPチップセットを開発, スマートコンタクトレンズに採用

https://www.ramxeed.com/jp/news-and-updates/4287/