アナログASICにおけるRF技術の基礎と設計アプローチ

アナログASICにRF技術を統合する意義と設計上のポイントを体系的に解説します。RFブロックの構成やノイズ対策、設計上の注意点などを具体的に示し、基礎から応用まで理解できる内容です。

アナログASICとRF回路統合の意義

アナログASICにRF回路を組み込むことで、特定アプリケーション向けに最適化された集積化デバイスを実現できます。これにより、高集積・小型化・低消費電力化を同時に達成できるため、IoTや通信機器など幅広い分野での製品競争力を高める設計が可能となります。

アナログASICとは何か:役割と特徴

アナログASIC(Application Specific Integrated Circuit)は、特定の機能に最適化されたアナログ回路を集積化するICです。汎用ICでは実現困難な高精度や広ダイナミックレンジ、低ノイズ特性を要求されるアプリケーションにおいて使用されます。プロセス選定やトポロジーの自由度が高く、A/D変換や信号整形、フィルタリング、電源管理など、多岐にわたる機能を単一チップに統合できます。また、システムレベルでの最適化が可能で、トータルコストの削減や回路面積の縮小にも貢献します。製品ごとの要件に合わせて設計されるため、用途に応じた高信頼性や長寿命性の確保にも優れています。

RF回路をASICに取り込むメリットと制約

RF回路をアナログASICに統合することで、部品点数削減や信号品質の向上、小型化などのメリットが得られます。特に高周波信号のルーティングにおけるノイズ混入リスクを抑える効果があり、ボード外配線による損失を回避できます。一方で、設計・検証の難易度は格段に高くなり、EMC対策や寄生素子の影響を予測した精密なレイアウト設計が求められます。また、RFブロック特有の温度変動やプロセスばらつきに対する対策も必須です。ASIC化に際しては、チップサイズや消費電力、RF性能のバランスを適切に取るためのアーキテクチャ選定が設計品質を大きく左右します。

RF CMOSや混載技術における設計動向

近年のRF設計では、CMOSプロセスによる高周波回路の集積化が急速に進展しています。RF CMOSは低コストでの大量生産が可能で、システムオンチップ(SoC)設計との親和性が高い点が評価されています。ただし、高い周波数領域では性能面でBiCMOSやSiGeに劣る場合もあり、技術選定には用途に応じた慎重な判断が必要です。また、アナログ・RF・デジタルを1チップに統合する「混載設計」も増加しており、ノイズ分離のためのレイアウト戦略や電源アイソレーション技術が重要視されています。設計者には、プロセス技術とアーキテクチャの最適な組み合わせを選択する能力が求められています。

RFアナログASIC設計の主要チャレンジ

高周波アナログASICの設計では、信号品質を確保しながらも物理的な制約を乗り越える必要があります。ノイズや発振などの影響を最小限に抑えるための多角的なアプローチが不可欠です。

雑音/位相ノイズと線形性のトレードオフ

RFアナログ設計において、ノイズ性能と線形性はしばしばトレードオフの関係にあります。特にLNAやミキサーといった初段回路では、低雑音特性を追求するとゲインが増し、非線形歪の増加を招く可能性があります。また、PLLやVCOなどのクロック生成系では位相ノイズの抑制が重要ですが、消費電力や面積、ロック時間との兼ね合いが設計上の課題となります。これらのトレードオフを最適化するには、各ブロックの性能パラメータを正確に見積もり、全体のシステム性能に与える影響を踏まえて設計する必要があります。適切なフィードバック制御やフィルタリングも不可欠な要素です。

発振抑制、ループ安定化、帰還設計

高周波領域において、予期せぬ発振の発生は回路動作の致命的な障害となります。特に高ゲインのアンプ回路や負帰還構成を持つRFブロックでは、配線インダクタンスや寄生容量によるループ遅延が位相余裕を減少させ、不安定化を引き起こします。ループ安定化を図るためには、周波数補償手法の導入やBode解析による安定性評価が欠かせません。さらに、帰還経路の設計においては、信号経路と電源経路の完全な分離、レイアウト段階での帰還配線の最短化、適切なデカップリングが重要です。RF ASICでは、帰還経路の設計が回路の全体性能に直結するため、初期段階からの安定性確保が必須です。

配線結合・基板ノイズ・サブストレート結合対策

高周波信号が混在するアナログASICでは、配線間結合やサブストレートを介したノイズ伝播が大きな問題となります。特に、ミキサーやPLLなど高感度な回路は、基板内の他回路からの結合ノイズにより動作が劣化することがあります。このような影響を防ぐには、グラウンドプレーンの分割や深溝トレンチ構造の活用、サブストレートバイアスの最適化など、物理設計レベルでのノイズ隔離が必要です。また、アナログ領域とデジタル領域の電源分離、シールド配線、コモンモードノイズ抑制設計なども効果的です。最終的な信号品質は、これらの対策がどれだけ確実に実装されているかに大きく依存します。

代表的ブロックと設計方針

アナログASICにおけるRFブロックは、個別に高度な設計スキルを要する要素が多く、それぞれの性能最適化と集積化バランスが鍵となります。

LNA、PA、ミキサー、VCO/PLL設計の要点

RFブロックの中核となるLNA(低雑音増幅器)、PA(パワーアンプ)、ミキサー、VCO/PLLは、それぞれ固有の設計要件を持っています。LNAではNF(雑音指数)の低減と入力マッチング、PAでは出力電力と効率、ミキサーでは変換利得とLO漏洩抑制が重視されます。VCO/PLLにおいては、発振周波数の安定性と低位相ノイズが求められます。これらブロックは高い相互干渉性を持つため、独立最適化ではなく、システム全体での整合性を確保しながら設計することが必要です。さらに、RF ASICとして一体化する場合は、プロセス選定や電源分離の工夫が性能確保の鍵を握ります。

RF‑ADC/RF‑DAC統合の方式と設計選択肢

RF信号を直接デジタル領域に変換するRF-ADCや、デジタル信号を直接RF出力するRF-DACは、回路統合における新たなトレンドです。これによりミキサーを介さずに広帯域通信が可能となり、構成の簡素化や信号忠実度の向上が見込めます。しかし、RF-ADCでは高いサンプリング速度と分解能の両立、RF-DACではスプリアス抑制や出力インピーダンス整合が重要な設計要件です。選択するアーキテクチャ(例:SAR型、パイプライン型、ΔΣ型)や、アンチエイリアスフィルタの配置も性能に影響を与えます。これらブロックをアナログASICに統合する際には、デジタル領域との電源ノイズ干渉を抑える設計工夫が不可欠です。

電源回路、整流器、バイアス回路の設計上の注意点

RFブロックを安定動作させるためには、電源・整流・バイアス系の精密な設計が欠かせません。例えば、LDOやスイッチングレギュレータを用いた場合でも、出力ノイズが高周波回路に混入することで感度低下やスプリアスの発生を引き起こすことがあります。また、温度変動やプロセスばらつきに対しても安定したバイアス電圧を供給する必要があり、リファレンス回路やスタートアップ回路の設計信頼性も問われます。RF領域では、一般のアナログ回路以上に電源インピーダンスやリップル除去比が性能を左右するため、ノイズマージンを考慮した設計が重要です。さらに、バイアス電流源には温度補償や電源追従性の高い構成が求められます。

まとめ

アナログASICとRF技術の融合は、高性能・高効率な電子機器設計の中核を担います。本節ではその意義、設計上の要点、今後の展望を整理します。

アナログASICとRF設計の融合がもたらす技術的優位性

アナログASICとRF回路の融合は、機能集約による部品削減、小型化、消費電力の最適化を可能にします。とくにアプリケーション特化型のRF通信機器では、外付け回路の削減によるノイズ対策や高信頼性実現に大きく貢献します。集積化によりインピーダンス整合や信号経路短縮も実現され、信号劣化が大幅に抑制されます。また、設計自由度の高いASICを活用することで、最適な回路アーキテクチャを選択でき、システム全体の性能を最大化する道が拓かれます。

アナログRF設計で重視すべき信号品質と実装戦略

RF信号は微弱かつ高周波であるため、レイアウトや基板設計の影響を強く受けます。特に配線結合やサブストレートノイズによる干渉を防ぐためには、信号ラインのシールド、電源・グラウンド分離、基板材料の選定が重要となります。また、システムレベルでのEMC設計やフィルタリング手法の導入も不可欠です。信号品質の確保には、単なる回路設計だけでなく、物理設計・実装戦略の段階から総合的な最適化を行うことが鍵を握ります。

今後のアナログASIC活用における重要な設計的観点

アナログASICの活用が進む中で、求められるのは回路単体ではなくシステム全体の整合性を踏まえた設計的判断です。とくにRF機能の統合によって、電源・信号経路・基板レベルでの相互干渉や実装制約が顕在化しやすくなります。設計段階では、ノイズマージンや周波数分離、信号劣化のリスクを見積もりながら、アーキテクチャ選定やブロック分割を行うことが重要です。また、プロセス技術の選択や物理設計の自由度、長期供給性といった要因も全体の最適化に影響します。ASICによる高集積化は、性能と制約のバランスを精緻にとる設計判断が不可欠となる領域です。

FeRAM搭載アナログASICの設計・開発サービスについて

https://www.ramxeed.com/jp/products/asic-assp/

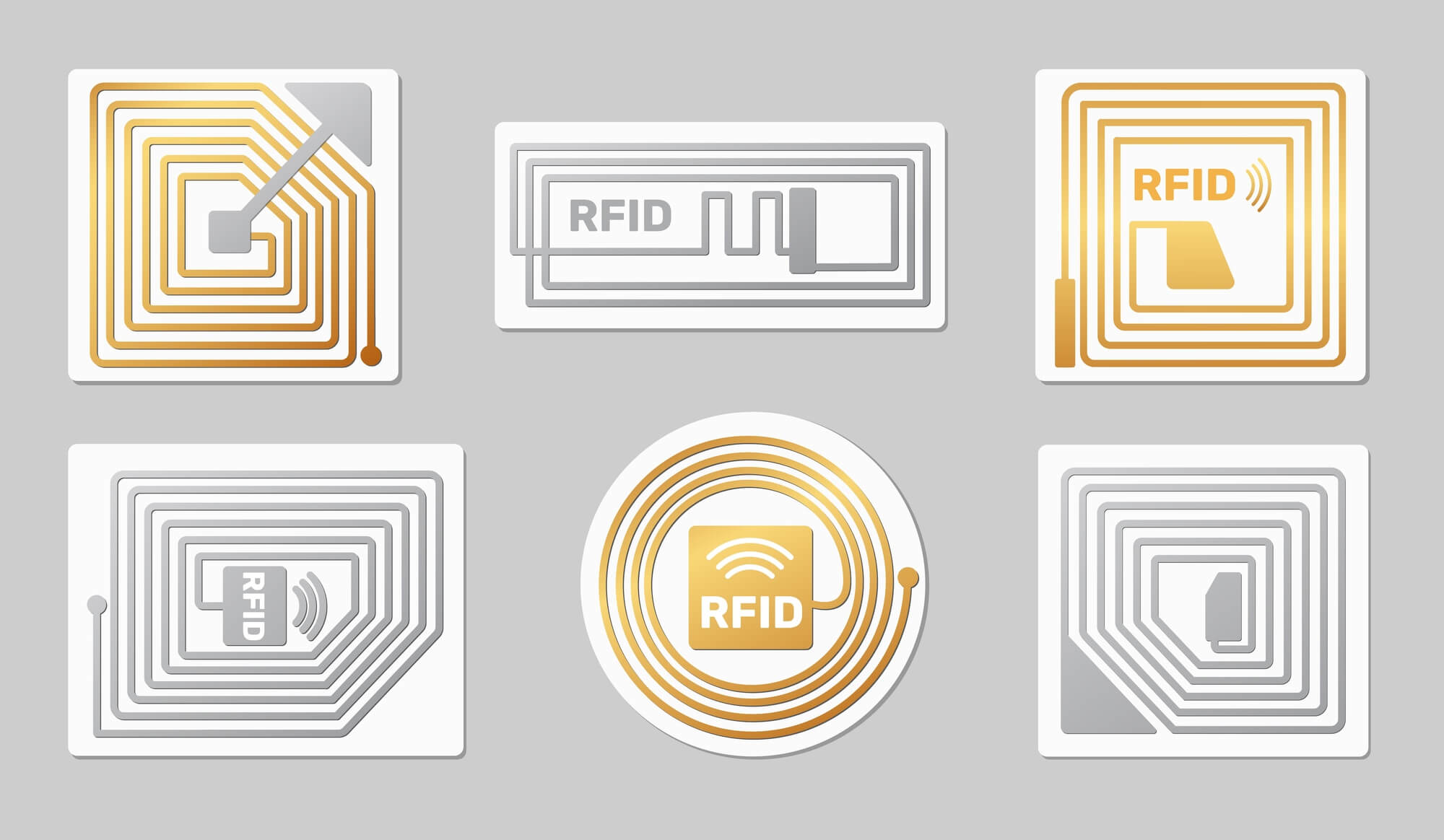

FeRAM搭載RFIDを選ぶ理由

https://www.ramxeed.com/jp/products/asic-assp/why-feram-rfids/

プレスリリース:FeRAM搭載ASSPチップセットを開発, スマートコンタクトレンズに採用

https://www.ramxeed.com/jp/news-and-updates/4287/