アナログ回路とデジタル回路の違いとASIC設計手法の基礎

ASICの基礎からアナログ・デジタル回路の違い、各設計手法の特徴までを専門的に解説します。フルカスタムやスタンダードセル、ミックスドシグナルの設計ポイントや応用分野も詳しく紹介し、設計の理解を深めます。

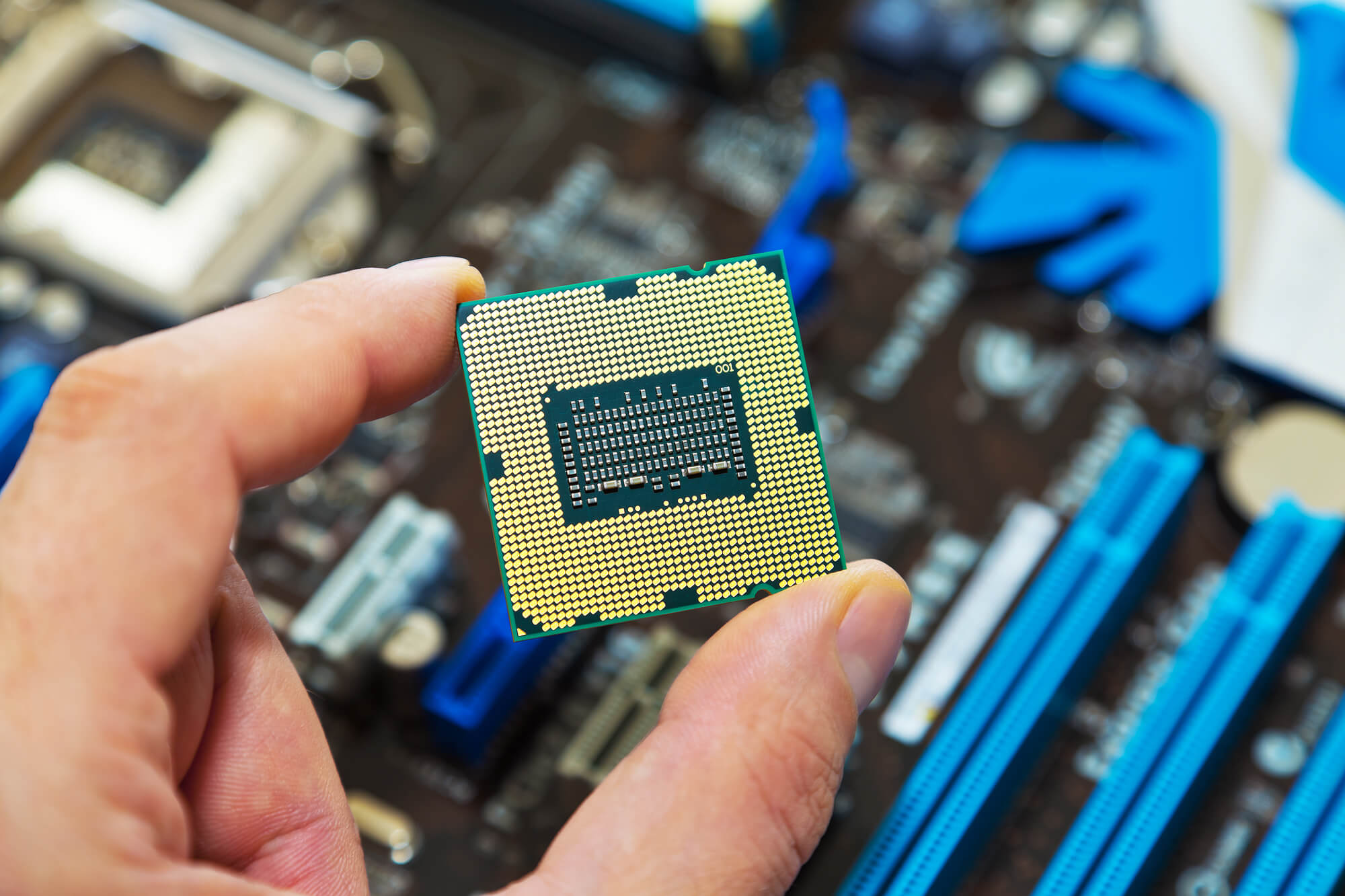

ASICとは何か

ASIC(Application Specific Integrated Circuit)は、特定用途の性能・電力・面積・コストを同時に最適化するために個別設計される集積回路です。汎用プロセッサやASSPに比べ、不要機能を排し必要機能をハードウェア化することで高い電力効率とスループットを実現します。一方でマスク費などの初期費用(NRE)が大きく、量産規模やライフサイクル、差別化要件の評価が採否を左右します。FPGAからの量産移行先としても選ばれ、アーキテクチャ設計が成功の鍵になります。

ASICの基本構造と分類(フルカスタム・スタンダードセル・ゲートアレイ)

フルカスタムASICはトランジスタレベルで回路とレイアウトを作り込み、回路方式・デバイスサイズ・配線まで最適化します。最高の性能・面積効率・低消費電力を得られますが、設計工数と検証負荷が大きく、再利用性が低い点が課題です。スタンダードセル方式はライブラリ化されたセルを配置配線で組み上げる主流手法で、設計期間と品質のバランスに優れます。ゲートアレイ(マスター・スライス)はトランジスタ配列を共通化し、金属配線のカスタムで短納期と低NREを実現しますが、性能自由度は相対的に低くなります。

アナログASIC・デジタルASIC・ミックスドシグナルASICの概要

アナログASICは増幅・フィルタ・基準電源・センサーインターフェースなど連続信号を扱う回路群で構成され、微小信号のS/Nやリニアリティ、温度・プロセス変動耐性が設計指標になります。デジタルASICは論理演算と状態制御を担い、並列化やパイプラインで処理スループットを引き上げます。ミックスドシグナルASICは両者を同一ダイに統合し、ADC/DAC、PLL、SERDES、DSPなどのブロックが協調動作します。統合時はクロストークや電源分離、クロックジッタ、タイミング整合が主要な設計課題になります。

ASICが活躍する分野と代表的な応用例

民生分野では画像処理エンジン、オーディオコーデック、電源管理ICが代表例で、熱設計と電池駆動時間の制約下でPPA(性能、消費電力、面積)の最適点を狙います。車載ではレーダー・カメラ向けフロントエンド、モータ制御、ゲートドライバなどで機能安全(ISO 26262)やAEC-Q準拠が重要です。産業・医療では高分解能計測、超音波やバイオ信号処理、堅牢な通信が求められます。通信インフラでは5G/6Gのビームフォーミング、ベースバンド、光トランシーバでカスタム実装が効果を発揮します。

アナログ回路とデジタル回路の違い

アナログ回路は物理量の連続性を忠実に扱うため、素子ばらつき・温度・電源リップル・レイアウト寄生成分が直接性能に跳ね返ります。対してデジタル回路は論理レベルの離散表現により一定のノイズ余裕を確保しやすく、冗長化やエラー訂正を組み合わせやすい利点があります。ただし高速化に伴いSI/PI、ジッタ、ばらつきによるタイミング閉塞が顕在化します。両者の特性差を踏まえ、仕様・試験・量産性まで含めた設計判断が必要です。

アナログ回路の特徴(連続信号・精度・ノイズ感度)

アナログ回路は連続値を扱い、ゲイン、帯域幅、位相余裕、リニアリティ、PSRR、CMRR、ノイズ密度といった指標で評価します。設計では素子マッチングや温度係数、1/fノイズ、サブストレート結合、配線抵抗・容量の寄生影響を抑える工夫が欠かせません。ガードリング、シールド配線、差動化、チョッパ安定化、適切な基準生成などの手法でS/Nを確保します。測定でも環境・治具・校正の影響が大きく、シリコン前後の相関取りが品質を左右します。

デジタル回路の特徴(離散信号・速度・消費電力効率)

デジタル回路は0/1の離散レベルで表現し、論理再生により長配線でも誤りを抑制できます。性能はクロック周波数と並列度で伸ばせますが、動的電力P≈αCV²f、リーク電流、IRドロップ、EM、クロックツリー負荷が制約になります。電力最適化では電圧・周波数スケーリング、クロックゲーティング、パワーゲーティング、マルチVt/マルチVddが有効です。信頼性ではメタステ、ソフトエラー、加速寿命要因(BTI/HCI/EM)の管理が重要になります。

設計フロー・ツール・検証方法の違い

アナログは回路図設計→SPICE系解析(DC/AC/トランジェント/ノイズ)→レイアウト→PEX後再解析→シリコン評価と進み、コーナー・Monte Carloで変動を検証します。デジタルは仕様→マイクロアーキ→RTL記述→機能検証→論理合成→配置配線→STA→DFT→物理検証の自動化フローが確立しています。検証もアナログは測定相関重視、デジタルはシミュレーション網羅率・形式検証・CDC/RDCが鍵となり、テスト戦略も大きく異なります。

それぞれのASIC設計手法

選択する設計手法は目標PPA、数量、リスク許容度、スケジュール、将来の派生展開で決まります。アナログは素子物理とレイアウト工学を駆使し、モデルの限界を実測で埋める反復が中心です。デジタルはEDA自動化で大規模化に対応し、検証計画が品質のボトルネックになります。ミックスドシグナルでは両者の前提が衝突するため、フロアプランや電源分割、解析レベルの統一が成功の前提になります。開発体制とIP戦略の整合も必須です。

アナログASIC設計の流れ(SPICE解析・レイアウト・アナログ検証)

まず仕様からアーキテクチャを選定し、素子サイズとバイアス条件を見積もります。次にSPICEでDC/AC/トランジェント/ノイズ/モンテカルロ解析を実施し、温度・電源・プロセスのコーナーを網羅します。レイアウト段階ではマッチング、対称性、ルーティング抵抗・容量、サブストレートカップリングを管理し、ガードリングやメタルシールドを適用します。PEX後に再解析して安全余裕を確認し、シリコン評価では計測系誤差まで含めた相関取得を行います。

デジタルASIC設計の流れ(RTL設計・論理合成・タイミング解析)

仕様を元にマイクロアーキテクチャを定義し、RTLで機能を実装します。静的解析(Lint/CDC/RDC)とシミュレーションで早期不具合を除去し、合成でセルマッピング後に配置配線で物理効果を折り込みます。STAでセットアップ/ホールド、OCV、クロック不均一、IR/EM制約を検証し、電力解析で動的・漏れを最適化します。DFTではスキャン挿入、BIST、ATPGパターン生成を行い、サインオフDRC/LVS/PEXを経てテープアウトへ進みます。

ミックスドシグナルASIC設計の特徴と設計課題

MS設計ではアナログとデジタルの干渉最小化が最重要です。電源/グラウンドを領域分割し、帰還ループとクロック配線を短く、感度の高いノードはシールドします。フロアプランはサブストレート結合を見越して配置し、デカップリング容量を戦略的に配します。検証はAMSコシミュレーション、RNM(wreal等)、等価モデルで階層化し、インターフェースの時相・メタデータ整合を網羅します。量産段階ではテストの観測性とキャリブレーション機構の準備が有効です。

まとめ

アナログは連続信号の忠実度、デジタルは離散信号の堅牢性という本質差が設計のアプローチを決定します。要求仕様のどこに性能ボトルネックが潜むかを見極め、適切な回路方式と設計手法を選ぶことがPPA最適化と品質確保の近道です。量産時の測定性やテスト容易化も初期から織り込み、アーキテクチャ・IP・プロセス選択を一貫して整合させる視点が重要になります。

アナログとデジタルの違いを理解する重要性

両者の特性差を正しく理解すると、仕様の優先度付けや妥協点の設定が明確になります。たとえばS/Nを重視するならアナログのレイアウトと基準源が支配的であり、スループットを重視するならデジタルの並列度とクロック階層が鍵です。この理解は、IP選定、シミュレーション計画、評価治具設計、歩留まり改善の各局面で正しい投資判断につながり、開発リスクの早期低減に寄与します。

それぞれの設計手法を押さえるメリット

アナログ手法を押さえることで実シリコンのばらつきや計測起因のズレに強くなり、試作回数と評価工数を削減できます。デジタル手法を体系化すれば、検証網羅率の向上と自動化の活用で大規模設計の品質を安定化できます。両者を横断的に理解すれば、ミックスドシグナル化やチップ分割・SiP化の判断が適切になり、製品ロードマップ全体でのコスト最適化に直接効きます。

今後のASIC設計に求められるスキルと視点

今後はシステム視点でのアーキテクチャリング、低消費電力と熱設計、先端パッケージ(2.5D/3D、SiP)、セキュリティ、信頼性(ASIL/機能安全)、製造ばらつきと経年劣化のモデリングが重要になります。さらに、AMSコシミュレーションや形式検証、DFT/DFM、量産データ解析まで含めた“設計~製造~フィールド”のループを回せることが競争力です。回路やセンサーなど周辺IPとの協調最適化も価値創出の中心になります。

FeRAM搭載アナログASICの設計・開発サービスについて

https://www.ramxeed.com/jp/products/asic-assp/