ASIC/FPGA/CPLD の設計アプローチを理解し、最適活用するための比較ガイド

ASIC、FPGA、CPLDの設計アプローチを比較し、製品要件に応じた最適な選定判断を支援します。半導体設計エンジニアが性能、コスト、供給面を正確に見極められる内容です。

目次

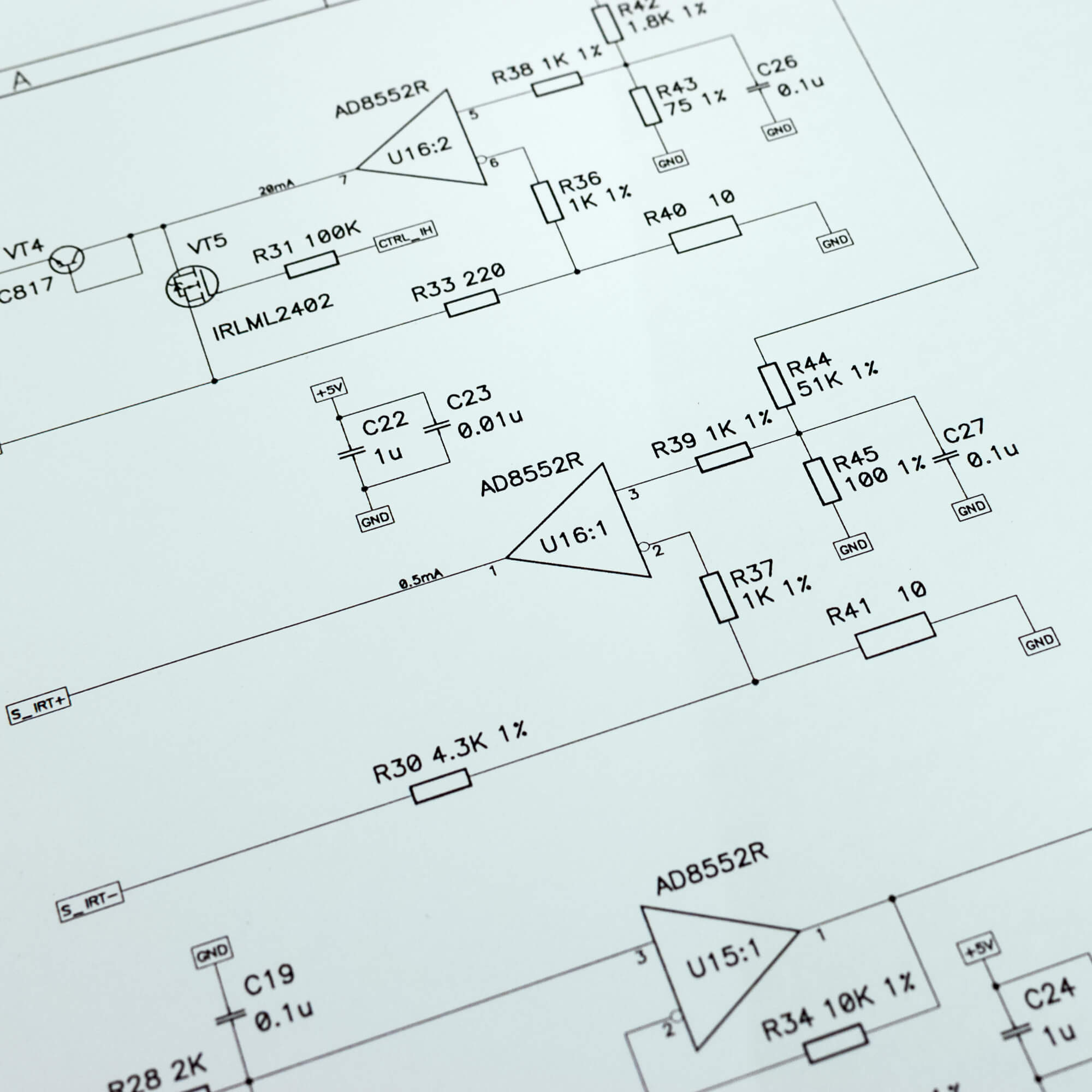

それぞれのデバイスアーキテクチャと設計アプローチの違い

デバイス選定の第一歩は、それぞれの構造的特徴と設計アプローチの違いを理解することから始まります。ASIC、FPGA、CPLDは内部構造や再構成性、用途に明確な違いがあります。

ASICの設計思想と適用範囲

ASIC(Application Specific Integrated Circuit)は、特定用途向けに最適化された集積回路であり、動作仕様に応じた論理回路をトランジスタレベルで実装します。高い性能・低消費電力・小型化を同時に実現できる一方で、初期開発費用や設計工数は非常に大きくなります。設計完了後の変更が不可能であるため、事前の仕様確定と検証フェーズが極めて重要です。特に、量産品においてはコストパフォーマンスが高く、製品寿命が長い場合に真価を発揮します。

FPGAの柔軟な再構成性と使い所

FPGA(Field Programmable Gate Array)は、構成可能な論理セルと配線リソースを持つ再構成可能デバイスです。開発者が設計データを使って構成を自由に変更できるため、プロトタイピングや短納期製品に最適です。近年のFPGAは高性能化が進み、AI・エッジ処理・画像解析など計算集約型アプリケーションにも適用可能です。ただし、ASICと比較すると消費電力・チップサイズ・動作周波数の面で劣る場合があります。開発柔軟性と実行性能のバランスを見極める必要があります。

CPLDのシンプル設計と制御用途での活用

CPLD(Complex Programmable Logic Device)は、比較的小規模な論理回路を実装するためのプログラマブルデバイスで、決まった構造と固定された配線アーキテクチャを特徴とします。FPGAに比べて再構成性やリソース量は限定されますが、起動が高速で低消費電力である点が魅力です。タイミング制御、I/O制御、シリアル通信の制御ロジックといった比較的単純な処理に適しており、マイコンやセンサ周辺の補完回路として利用されることが多くなっています。

性能・コスト・消費電力の観点からみた選定指標

デバイスの性能やコスト構造、消費電力の違いは、製品要件との整合性を取る上で重要な判断軸となります。それぞれの指標のバランスを理解しておく必要があります。

設計初期費用と量産時のコスト構造の違い

ASICは、マスク費用やNRE(Non-Recurring Engineering)費用が非常に高額で、設計ミスの修正も困難なため、初期費用が突出しています。一方、FPGAやCPLDは初期投資が小さく、サンプル単位での設計試作が可能です。量産段階においては、ASICは1個あたりの単価が大幅に下がるため、万単位の製品数を想定する場合に圧倒的なコスト優位性を発揮します。逆に、小ロットまたは短期製品では、柔軟性のあるFPGAやCPLDが適します。

処理速度・電力効率・熱設計の比較

ASICは、トランジスタレベルで最適化できるため、動作速度と電力効率で他のデバイスを大きく上回ります。FPGAは構成セル間の配線遅延やロジックのオーバーヘッドがあるため、クロック周波数や消費電力で制限を受けやすいです。CPLDは機能規模が小さく、クロック動作が限定的な分、消費電力は比較的抑えられます。製品設計においては、筐体内の熱制約やバッテリー駆動時間なども含め、電力制御と熱設計の観点からの選定が求められます。

設計密度とチップ面積、実装制約の観点

ASICは、特定用途向けにトランジスタ配置までを制御できるため、非常に高密度な設計が可能です。FPGAは論理セル単位の設計になるため、同じ機能を実装しても面積が大きくなりがちです。CPLDは、あらかじめ決まったマクロセルを組み合わせて構成されるため、設計密度は限定的ですが、シンプルで実装しやすいという特徴があります。実装サイズやパッケージ形状、周辺部品との配置関係を考慮し、各デバイスの物理的特性を理解しておくことが重要です。

開発工程における柔軟性とリスク管理の考慮点

設計から製造に至るまでの開発フローでは、柔軟性や修正対応力が開発リスクと直結します。スケジュールや品質の観点から各デバイスの特性を見極めることが求められます。

開発期間・ツール・IP資産の活用性

FPGAやCPLDは設計後すぐに書き込み・動作確認が可能であり、短期間での開発が実現できます。豊富な開発ツールや既成のIPコアを利用できるため、製品仕様の変動にも柔軟に対応できます。ASICの場合、開発期間が長く、RTL設計から物理設計、レイアウト、DRC/LVSチェックなど複雑な工程が必要です。高性能なEDAツールの使用が前提となり、設計資産の再利用性や知財管理も重要な観点になります。プロジェクトのスケジュール管理において、この違いは大きな要素です。

設計修正・リビジョン対応力と量産信頼性

FPGAとCPLDは設計データを再構成することで、リビジョン変更やバグ修正を即座に行えます。特に量産前の実証実験や顧客要望のフィードバック対応が求められるアプリケーションでは、この柔軟性が強みとなります。一方で、ASICは一度設計・製造が完了すると、物理的な修正はできません。そのため、仕様凍結後の変更ができず、事前検証とシミュレーションの精度が設計成功の鍵を握ります。品質の安定性と信頼性確保を目的とするならば、ASICは最も優れた選択肢です。

検証・プロトタイプ・市場投入のスピード感

開発初期段階におけるスピード感では、FPGA/CPLDが圧倒的に優れています。すぐに書き込み・実行できる環境が整っており、社内のソフトウェアエンジニアやアプリケーション開発チームと連携しながら、動作検証を短期間で行うことが可能です。ASICは一連の開発フローを順次踏む必要があり、試作品の製造に数ヶ月単位のリードタイムが必要です。製品の市場投入スピードを重視する場合は、まずFPGAで開発・検証を行い、その後にASIC化する流れが一般的です。

ASICを活用する際の実務的チェックポイント

ASICは高性能かつ量産向けの最適解となる一方で、設計・製造の各フェーズでの実務的な判断が製品成功の鍵を握ります。導入に際して押さえるべき要点を整理します。

採用するプロセス技術と設計資産の整合性

ASIC開発では、ターゲットとする製品の要件に対して最適なプロセス技術を選定することが不可欠です。消費電力や性能、コストなどの制約条件に応じて、28nm以下の先端プロセスを用いるか、信頼性・安定供給を重視した65nmや130nmなどの成熟ノードを採用するかの判断が求められます。さらに、利用可能な標準セル、I/Oライブラリ、電源分離対応、ESD保護などの設計資産が、回路構成やインターフェース要件に適合するかも重要です。eFlashやFeRAMなどの不揮発性メモリやアナログ・ミックスドシグナルの統合が必要な場合、それらに対応可能な設計手法・IP構成の確認も欠かせません。

コスト構造と製造工程に関する技術的理解

ASICの製造には、設計データ作成からマスク作成、ウェハ製造、後工程(組立・テスト)まで、複数の工程が関与します。なかでもマスク作成に関わる初期費用(NRE)はプロセスノードの微細化に伴い大きくなる傾向があり、設計段階での繰り返し修正を抑える工夫が必要です。開発初期においては、MPW(Multi Project Wafer)などの手法を用いて試作コストを低減する選択肢もあります。さらに、歩留まりの予測、検査手法、テストポイント設計、組立時のパッケージ制約など、各工程に潜在するコスト要因と技術的条件を事前に把握しておくことが、開発リスクの低減につながります。

量産体制と長期供給に向けた設計上の配慮

製品の商用展開を見据えた際には、量産体制の確立と継続的な供給が実現可能かを設計初期から意識する必要があります。たとえば、量産後の再設計を想定したDFT(Design for Testability)や冗長構造の導入、プロセスバリエーションに対するマージン設計などが挙げられます。また、産業用やインフラ機器など長期供給が求められるアプリケーションにおいては、プロセスノードのライフサイクル(EOL予測)やIPライセンスの持続性を考慮する必要があります。加えて、バックアップファウンドリの想定、レイアウトの移植性、パッケージの汎用性といった冗長性設計が、長期にわたる製品安定供給の鍵となります。

まとめ

ASIC、FPGA、CPLDはそれぞれ異なる設計アプローチと構造的特徴を持ち、用途や開発条件に応じて最適な選択肢が異なります。高集積・低消費電力・高性能を追求するのであればASICが有力ですが、設計初期の柔軟性や開発スピードを重視する場合には、FPGAやCPLDの活用が現実的です。とくにASICの採用にあたっては、プロセス選定、設計資産との整合性、コスト構造、長期供給の見通しまで、技術的な観点からの総合的な検討が求められます。各デバイスの特性を正しく理解し、製品のライフサイクルや市場要件に応じた設計戦略を立てることが、確実な開発成果へとつながります。

FeRAM搭載アナログASICの設計・開発サービスについて

https://www.ramxeed.com/jp/products/asic-assp/