ミックスドシグナルIC設計の基礎と実践技術:ノイズ対策から応用例まで

ミックスドシグナルICの構成要素や役割、設計時に直面するノイズやクロストークなどの課題と対策、PCB実装での領域分離やグランド設計の基本、最新技術動向や活用リソースまで体系的に解説します。

目次

はじめに:ミックスドシグナルICの全体像

ミックスドシグナルICは、アナログ信号とデジタル信号の処理機能を1つの半導体チップに統合した集積回路です。アナログ部分は電圧や電流など連続的な物理量を扱い、デジタル部分はそれを論理的に制御・演算・記録します。この統合により、回路規模の削減、小型化、省電力化、高速化が可能となります。代表的な用途はスマートフォンの通信機能、車載制御ユニットのセンサ処理、医療機器の信号解析などです。アナログとデジタルが混在することで生じる設計課題を踏まえ、性能を最大限に引き出すための基本的な要素を理解することが重要です。

ミックスドシグナルICとは何か?

ミックスドシグナルICは、異なる性質を持つアナログ回路とデジタル回路を同一シリコン上に配置し、入出力信号の変換や処理を統合するものです。アナログ回路は外部信号を変換・増幅・フィルタ処理し、デジタル回路はそのデータを論理演算や制御アルゴリズムで処理します。単一チップ化により、信号経路が短くなりノイズの影響が減少し、消費電力や遅延も低減されます。多機能化や高速化が求められる現代の電子機器において、性能と効率の両立を可能にする中核技術です。

デジタルとアナログの役割

アナログ回路はセンサやアンテナからの連続信号を正確に扱い、必要に応じて増幅や帯域制限を行います。これをADC(A/Dコンバータ)がデジタル信号へ変換し、デジタル回路が制御・計算を実行します。制御結果を物理系に戻す際はDAC(D/Aコンバータ)が必要です。デジタル部分は柔軟な機能変更や複雑な演算を得意とし、アナログ部分は高感度・高精度の信号処理に適します。この役割分担によって、多様な機能を効率的に実装できます。

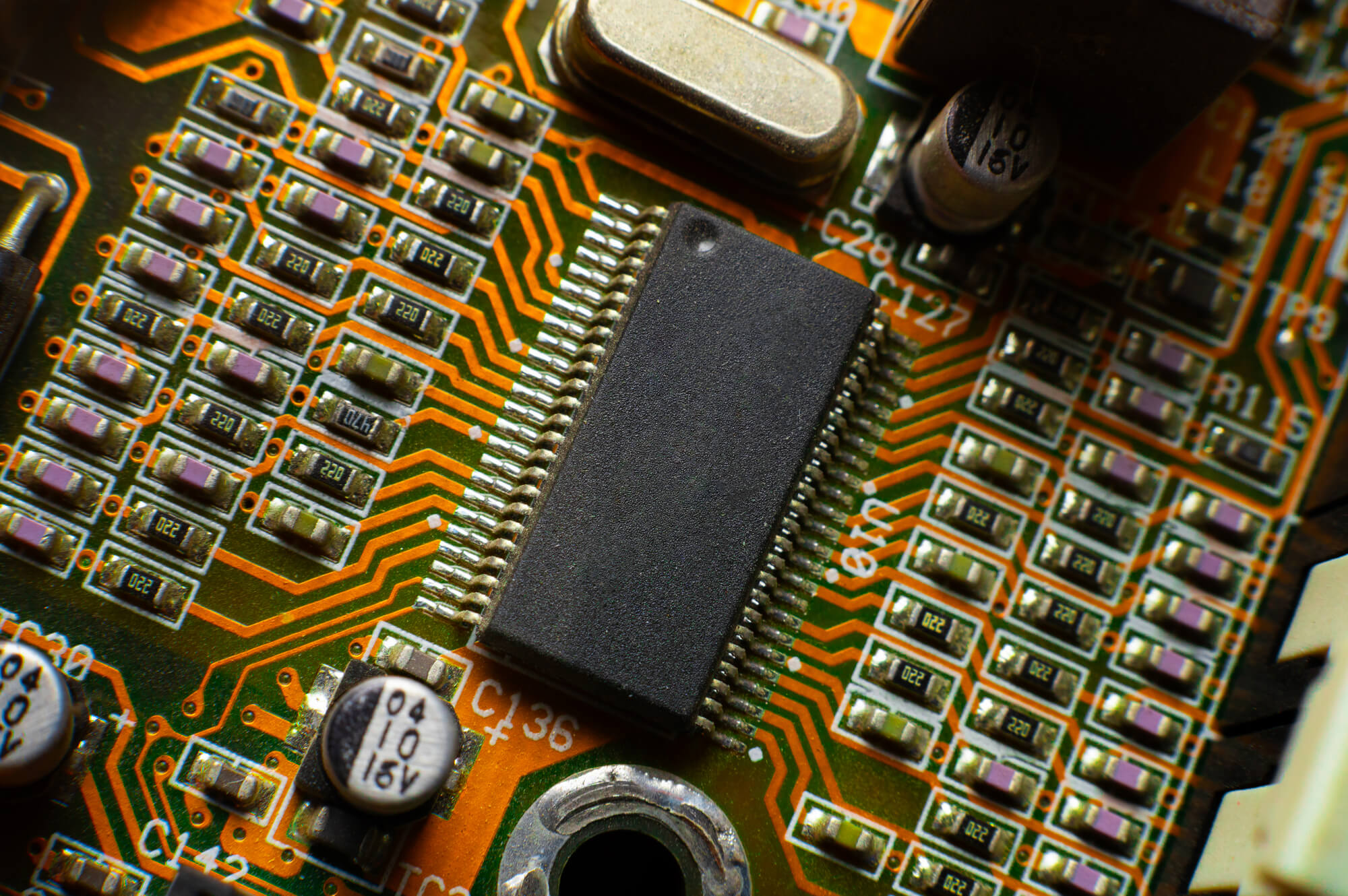

主要な構成要素

代表的な構成要素には、ADC、DAC、PLL(位相同期回路)、電源管理回路、RF CMOSブロックがあります。ADCはアナログ信号をデジタルに変換し、DACは逆変換を行います。PLLは安定したクロックを生成し、回路間の同期を確保します。電源管理回路は各ブロックへ適切な電圧・電流を供給し、安定動作を支えます。RF CMOSは無線通信や高周波信号処理を可能にします。これらが連携することで、多機能で高効率なシステムが実現します。

主な応用分野

IoT機器では低消費電力でセンサ計測と無線通信を統合し、電池駆動で長時間稼働します。車載分野では温度や振動などの厳しい条件下でも安定動作し、リアルタイム応答性が求められます。医療機器では心電図や超音波などの高精度信号処理が必須です。通信分野では高周波信号処理と高速デジタル制御を統合し、ネットワーク機器やモバイル端末の性能向上に貢献します。各分野で共通するのは、アナログとデジタル統合による信号品質の向上と省スペース化です。

設計時の主な課題と基本的な対策

アナログとデジタルの動作特性差により、ノイズ混入やクロストーク、電源品質低下が生じやすくなります。ノイズはデジタルのスイッチング動作や電源変動から発生し、アナログ精度を損ないます。これを抑えるには、アナログとデジタル領域を物理的に分離し、帰路の制御と適切なデカップリングを行う必要があります。クロストークは配線や基板構造を介して発生するため、信号経路分離やインピーダンス管理が有効です。電源品質は階層的デカップリングや専用電源ドメインで改善できます。

ノイズとグランド設計

ノイズ干渉を最小化するには、低インピーダンスで連続性のあるグランド面を確保し、アナログとデジタルの帰路を計画的に制御する必要があります。グランドを完全に分離すると帰路が長くなり、高周波特性が悪化する場合があります。そのため、多くの設計では単点接続やゾーニングを採用し、高周波成分の回り込みを抑制しながら安定した帰路を確保します。設計初期にグランド構造を計画しておくことが、最終性能の安定化に直結します。

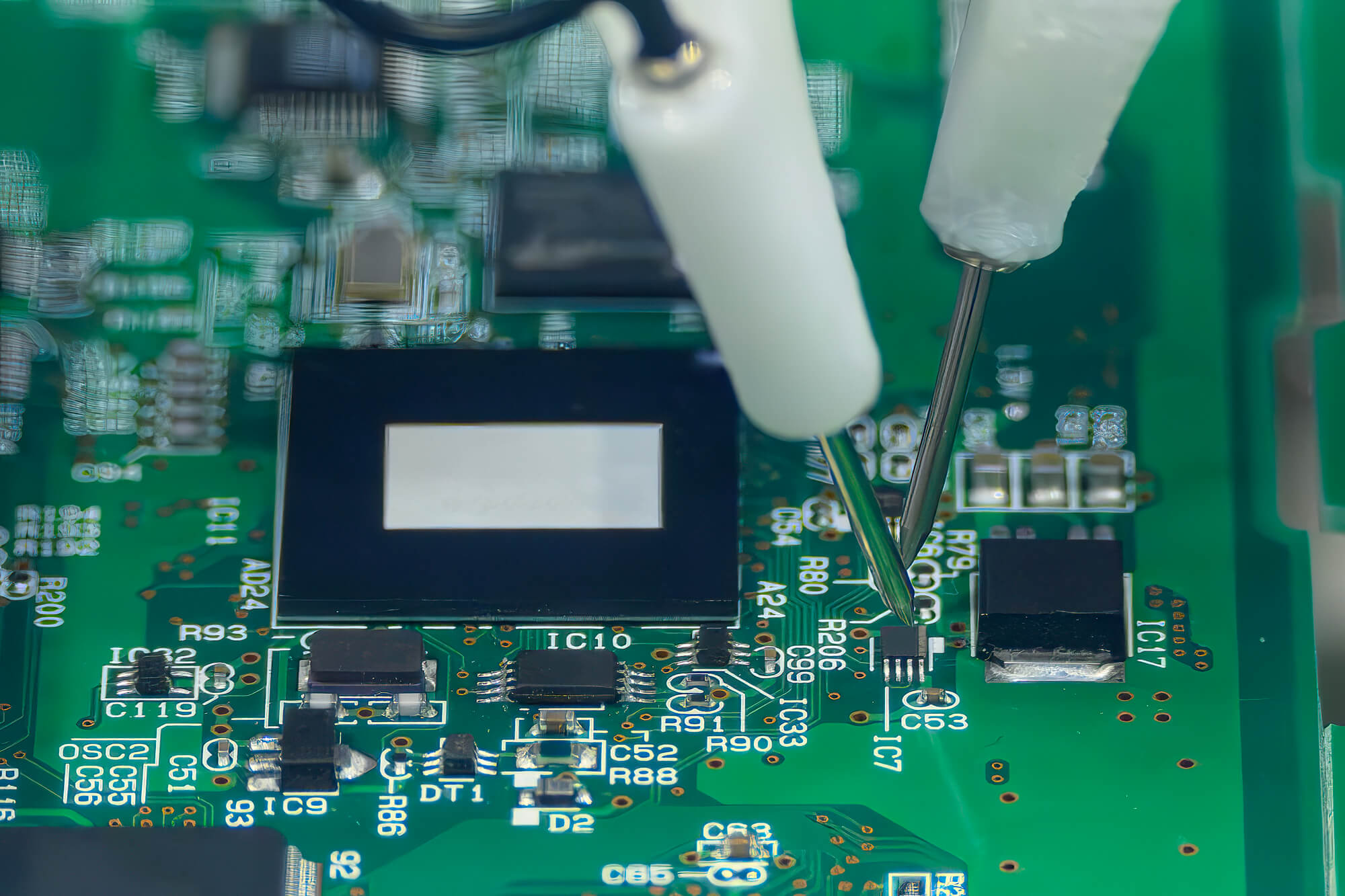

シミュレーションと検証

混載回路の検証には、Verilog-AMSなどの設計言語でアナログとデジタルの動作をモデル化し、全体挙動を再現する手法が有効です。これにより、実装前に干渉や性能劣化のリスクを検出できます。さらに、シンボリックモデルを用いれば安定性や感度を解析的に評価でき、設計の方向性を早期に判断可能です。これらの検証は物理設計前に行うことで、試作回数を減らし、開発期間を短縮します。

クロストークと電源管理

クロストークは、近接した信号経路や基板寄生要素によって発生し、誤動作や性能低下の原因となります。これを防ぐには、重要信号の経路を分離し、必要に応じてシールドを施します。電源管理では、負荷変動やスイッチングによるノイズを抑えるため、多段階デカップリングや電源ドメインの分離が有効です。特にアナログ回路には、クリーンな電源供給を行うことで、計測精度や安定性が確保されます。

PCB実装の基本的な考慮点

PCB設計では、シリコン内で確立した分離や電源計画を、実装レベルで破綻させないことが最重要です。アナログ/デジタルの配置分離、連続グランド面の確保、短い帰路、適切なデカップリング、特性インピーダンス整合、クロックや基準経路の最短化、電源ドメインごとの配電計画などを体系的に適用します。製品条件(温度、EMI/EMC、機構制約)を踏まえ、試作段階での測定・再配置を見越した余白も設け、量産ばらつきに耐える設計にまとめます。

領域分離

アナログとデジタルを明確にゾーニングし、ノイズ源(高速I/O、スイッチング電源、クロック)から感度の高い回路(ADC、基準、フロントエンド)を距離・シールドで守ります。ブロック間の信号流れと帰路を同時にマッピングし、ループ面積を小さく保つことが有効です。部品配置は入出力の近接、基準やセンサ経路の最短化、電源経路の直線化を優先し、検査点や治具アクセスも初期段階から確保します。これにより原因切り分けが容易になり、再設計の手戻りを抑制できます。

グランドの取り方

連続した広いグランド面を基準に据え、不要なスリットや分断を避けます。高周波では帰路電流が信号直下を通るため、分断は迂回と放射の増大につながります。アナログとデジタルの完全分割は慎重に検討し、重要信号は分断上を横切らせない規律を徹底します。ビアステッチやグランドヴィアの密度を要所に増やし、電源ピン近傍に低ESLのデカップリングを配置することで、帰路インピーダンスを一貫して低減できます。

配線と電源

高速信号は特性インピーダンスを設計し、差動ペアは間隔・長さ・層構成を揃えます。クロックや基準ラインは可能な限り短く、他のアグレッサから距離を取り、必要に応じてシールドやガードリングを施します。電源は周波数帯域を分担する複数値のコンデンサを近接配置し、電源ループを極小化します。アナログ/デジタルで電源ドメインを分け、LDOとスイッチングの役割を整理すると電源ノイズが抑えられます。IRドロップと温度上昇も並行評価し、設計余裕を確保します。

まとめ

ミックスドシグナルIC設計のポイント総括

ミックスドシグナルICの設計では、ADCやDAC、PLL、電源管理回路、RF CMOSなど主要構成要素の動作原理と役割を理解することが基礎となります。設計課題としては、デジタル高速スイッチングによるノイズ干渉、近接配線によるクロストーク、電源品質低下などが挙げられます。対策としては、アナログとデジタルのゾーニング、帰路を制御したグランド設計、信号経路のインピーダンス整合が有効です。これらを組み合わせることで、量産時の性能安定と設計初期からの品質確保が可能になります。

今後のトレンドと技術動向(AI支援設計、チップレット)

EDAツールとAI技術の融合により、回路配置やパラメータ最適化の自動化が急速に進んでいます。特にAIは、膨大な設計パターンから最適なゾーニングや配線ルートを提案し、設計時間短縮と性能向上を両立します。さらにチップレット技術では、アナログとデジタルを別ダイとして最適プロセスで製造し、パッケージ内で高密度接続する手法が注目されています。これによりプロセス選択の自由度が増し、コスト効率や信頼性向上にも寄与します。

設計者へのおすすめリソース(ツール、文献)

ミックスドシグナルICの理解を深めるには、Verilog-AMSによる混載回路モデリングや、シンボリック解析ツールによる安定性評価の経験が有効です。メーカーによってはアプリケーションノートに実装課題と解決策を具体例付きで解説しているところもあり、実務に直結します。さらにアナログ・デジタル混載設計の基礎書籍やPCBレイアウト技術書を併読することで、設計検討の幅が広がります。これらの知見は設計初期段階から役立ちます。

FeRAM搭載アナログASICの設計・開発サービスについて

https://www.ramxeed.com/jp/products/asic-assp/