低消費電力アナログASICの基礎と設計考慮点:製品への組み込みに向けた技術的視点

アナログASICを製品に組み込む際に求められる低消費電力設計の基礎と実装上の注意点について解説します。FRAM(FeRAM、強誘電体メモリ)活用による電力最適化や回路レベルでの工夫も紹介します。

目次

アナログASICとは何か?製品開発での利用を前提とした基礎知識

アナログASICは、製品ごとの用途や動作条件に応じて最適化されたアナログ回路を統合した専用チップです。標準品では対応しきれない消費電力やサイズ、信号特性への要件を満たす設計が可能で、電力制約のある製品でも効率的な構成が可能となります。基本的な概念とメリットを理解することで、製品要件に最適な技術選定が行いやすくなります。

アナログASICの特徴とメリット:汎用ICとの違い

アナログASICは、用途に特化した機能のみを集積することで、不要な消費電力や回路規模を抑えることが可能なカスタムICです。汎用ICでは多くの機能が予備的に搭載されており、実際には使用されない機能の分だけ消費電力や基板面積が無駄になります。アナログASICではこうした無駄を排除し、精度、応答性、ノイズ耐性といったアナログ特性を必要最低限の電力で実現できます。また、部品点数の削減により信頼性の向上やコスト最適化にも寄与します。低消費電力とコンパクト化を同時に実現できる点が大きな強みです。

低消費電力の重要性:システム全体での電力制約

低消費電力設計は、ポータブル機器やIoT機器などバッテリー駆動が前提となる製品で特に重要です。アナログブロックは常時動作することが多く、回路構成やバイアス条件の最適化が消費電力の差に直結します。システム全体での電力予算が厳しい場合、アナログASICを利用することで必要な機能に絞った効率的な消費電力制御が可能になります。待機時、測定時、通信時など、製品の使用シナリオごとに異なる電力モードを想定し、それに応じた動作最適化が求められます。アナログASICの導入により、より高い精度を維持しつつ低消費を実現できるようになります。

アナログASICの活用が効果的なアプリケーション例

アナログASICは、センシング、信号増幅、電源監視、変換処理など、アナログ特性が重要となる機能を持つ製品で特に効果を発揮します。たとえば、医療用モニタリング機器では微小な生体信号をノイズ少なく増幅する必要があり、汎用品では精度・応答性が不足する場合があります。また、工業用センサやバッテリーマネジメントシステムのように、低電力かつ安定した制御が必要な分野では、専用化による低消費電力と信頼性の両立が可能です。用途ごとに必要な性能を的確に実現し、長期稼働や高耐久性が求められる製品群との親和性が高いといえます。

低消費電力アナログASICの設計技術とその影響

アナログASICでの低消費電力設計は、電気的性能とのバランスを取りながら行う必要があります。単純に消費電力を下げるだけでなく、応答速度やノイズ特性を維持するための工夫が求められます。製品の利用シーンや使用環境に応じた動作モードの設計が、電力効率の鍵を握ります。

回路レベルでの低消費化技術:電源制御・電流制限

アナログASICでは、バイアス電流や電源電圧の調整を通じて、細かいレベルでの消費電力最適化が可能です。たとえば、スリープモードやローパワーモードを回路ごとに持たせることで、使用時以外のブロックを停止し、無駄な電力を削減します。さらに、電源電圧の最小動作限界を下げることで、システム全体の電力設計に余裕が生まれます。過剰なバイアス設計は信号忠実性を上げる反面、不要な電力消費を招くため、アプリケーションの必要精度に見合ったチューニングが重要です。こうした調整は、回路シミュレーションと評価の繰り返しで確実なものになります。

アナログブロックの消費電力最適化:ADC、アンプなどの例

アナログASIC内の主要ブロックであるADCやアンプは、電力設計上大きな影響を与える要素です。これらの回路には、用途ごとに最適なアーキテクチャを選定することが求められます。たとえば、高速応答が不要なセンサ用アンプではスルーレートを抑えて電流を節約でき、高速変換を必要としないADCでは逐次比較型を採用することで消費電力を大幅に低減できます。また、オペアンプのバイアス電流やゲイン設定、シャットダウン機能の有無など、細かなパラメータが最終的な電力に影響を及ぼします。ブロック単位での最適化が進めば、全体としての電力効率を大きく改善できます。

低消費電力と性能のトレードオフ:利用者が知っておきたい制約

アナログASICにおける電力最適化は、設計自由度の高さと同時にトレードオフの理解が不可欠です。電流を抑えることで消費電力は下がりますが、応答速度やゲイン帯域積が制限されることがあります。また、低電圧動作では出力スイングが制限され、入力電圧範囲との兼ね合いにより信号の忠実性が損なわれる可能性もあります。さらに、プロセスばらつきや温度変動に対する余裕が小さくなるため、設計マージンの見極めも重要です。製品ごとにどの性能を最優先するかを明確にし、その条件に最適化された設計方針を選ぶことが成功の鍵となります。

製品設計においてアナログASICを活用する際の考慮点

アナログASICを製品に組み込む際は、単体の回路性能だけでなく、システム全体との整合性や実装上の要件にも注意を払う必要があります。要件定義、インターフェース、実装時の対策までを見据えて設計を進めることで、安定した動作と消費電力の最適化が可能となります。

要件定義のポイント:電力、精度、応答速度の整理

製品設計の初期段階で、アナログASICに求める性能要件を明確にしておくことは非常に重要です。たとえば、使用環境や動作シナリオごとに、必要とされる応答速度、精度、消費電力の優先順位を設定することで、過剰仕様や性能不足を防ぐことができます。また、システム全体の電源設計に対して、どのタイミングでどのブロックが動作するかを整理することで、電力のスムーズな制御が可能になります。必要最小限の性能で最大の効率を得るには、このフェーズでの判断が最も重要です。

システム全体とのインターフェースを考慮した設計要素

アナログASICは他のICやセンサ、マイコンと連携して動作するため、I/O電圧の整合性や通信タイミングの調整といったインターフェース設計が不可欠です。特に、起動シーケンスやパワーマネジメントとの連携により、不要な電力消費や誤動作を避ける設計が求められます。また、ノイズやクロストークへの耐性を確保するため、信号経路やレイアウトの工夫も必要になります。全体システムの構成において、アナログASICがどの役割を担うかを明確にし、回路と機能の配置を最適化することで、より一層の省電力効果を引き出せます。

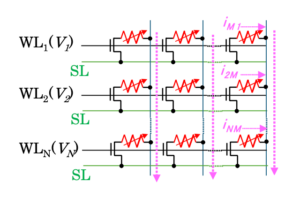

FRAMを組み込んだアナログASICの低消費電力活用例

アナログASICにFRAMを内蔵することで、さらなる低消費電力化とシステム簡素化が実現できます。FRAMはフラッシュメモリに比べて非常に低い電圧と短時間で書き込みが可能で、頻繁なデータ更新が必要な用途に最適です。たとえば、しきい値やキャリブレーションパラメータをFRAMに保持し、電源断後もデータを安全に保存することで、再起動時の動作も迅速かつ確実になります。外付けメモリが不要になることで、インターフェース回路の簡素化や部品点数の削減が図れ、信頼性の向上と消費電力の削減を同時に実現できます。FRAM搭載アナログASICは、次世代の省電力アーキテクチャにおける重要な構成要素となり得ます。

実装段階で起こりうる問題と事前の設計対策

アナログASICの実装では、シミュレーション上では現れない課題が顕在化することがあります。代表的なものとして、電源ノイズの影響、信号線間の干渉、熱分布によるバイアス変動などがあります。これらは、レイアウト設計、電源・グラウンドの配線、適切なデカップリングによって軽減可能です。また、初期試作段階での実環境評価により、量産時の不具合を未然に防ぐことができます。FRAMなどの内蔵回路を持つ場合は、動作周波数や書き込み電圧に対する評価も早期から実施しておくと、設計マージンを適切に確保できます。

製品設計に活かすためのアナログASIC低消費電力化の要点整理

アナログASICによる低消費電力設計では、初期の要件定義から詳細な回路設計、システム評価に至るまで、段階ごとに明確な判断と整合性のある設計方針が必要です。各段階での最適化を積み重ねることで、高性能かつ省電力な製品が実現できます。

要件定義時に整理すべき低消費電力設計の観点

要件定義フェーズでは、電力制限の厳しさ、製品の稼働モード、通信頻度、計測精度などを軸に設計目標を整理することが重要です。特に、消費電力の評価は動作時、待機時、スリープ時の各モードに分けて検討し、システム全体でのピーク電力と平均電力のバランスを見ながら調整する必要があります。この段階で過不足のない要件を設定することで、後の設計段階での手戻りを最小限に抑えることができ、トータルでの開発効率が向上します。

設計の進行に応じて意識したい電力最適化アプローチ

設計の進行に伴い、回路の詳細仕様やシミュレーション結果が揃ってくる段階では、定量的な消費電力評価を逐次行い、必要に応じて回路構成や制御手法を見直すプロセスが必要になります。ブロック単位での評価からシステムレベルでの再統合まで、段階ごとのフィードバックループを設計に組み込むことで、狙った電力性能が確実に実現できます。評価環境と試作品を用いた実機ベースの電力測定も並行して行うことが重要です。

今後の製品開発におけるアナログASIC活用の可能性と展望

低消費電力と高性能の両立は、今後のあらゆる製品分野で重要な開発課題となり続けます。アナログASICは、個別の製品仕様に合わせた柔軟な設計が可能であり、さらなる省電力化を実現する技術として大きな可能性を持っています。加えて、FRAMやMEMSなどの機能を統合したハイブリッド型アナログASICのニーズも増加しており、アプリケーションごとの専用最適化が加速しています。適切な技術選定と設計パートナーとの連携を通じて、アナログASICを戦略的に活用することが製品の競争力向上につながるでしょう。

FeRAM搭載アナログASICの設計・開発サービスについて

https://www.ramxeed.com/jp/products/asic-assp/