SRAMバッファの削減手法:FRAM直接書き込みによるデータ構造の最適化

組込み機器におけるSRAMバッファ削減の課題と解決策を解説します。FRAM(FeRAM、強誘電体メモリ)への直接書き込みを活用し、データ構造を最適化することで中間バッファを排除し、消費電力とメモリ使用量を同時に低減する設計手法を紹介します。

SRAMバッファ削減が求められる設計背景

組込み機器ではSRAM容量が限られ、通信、制御、演算が同時に走ると一時バッファが競合します。ログやセンサの連続記録ではコピーが増え、スタック枯渇や断片化を招きます。バッファ削減は性能と信頼性の両面で重要です。特に低消費電力MCUでは外部メモリ帯域も細く、不要なバッファリングは遅延と電力を悪化させます。

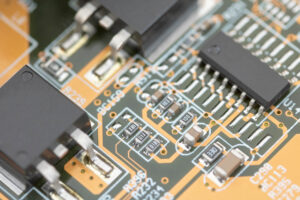

組込みシステムにおけるSRAM資源の制約

SRAMは低レイテンシでランダムアクセスできるため、割込み処理やDMAのワーク領域に多用されます。しかし容量は小さく、スタックとヒープが同一空間で競合します。通信スタックや暗号の一時領域を固定確保すると空きが減り、最大スタック量の見積りを誤ると境界条件で破壊が発生します。また、C言語の自動変数や一時配列を安易に使うと、実行経路によってピーク使用量が変動します。安全マージンを取るほどSRAMが逼迫し、機能削減か外付けRAM追加の判断に追い込まれます。

SRAMバッファ肥大化が引き起こす課題

バッファを増やすと欠損は減りますが、データを受信バッファから処理バッファ、さらに保存バッファへと複製するたびにメモリ帯域とCPU時間を消費します。キャッシュが小さいMCUではコピーがそのまま遅延になり、周期タスクの遅延(ジッタ)やデッドラインミスの原因になります。加えて電力が増え、熱や電池寿命にも影響します。また、バッファ境界の取り扱いが複雑化し、オフバイワンエラー(境界値の誤り)や排他制御の不備が潜みやすくなります。デバッグ時は内容が段階ごとに変形するため、不具合箇所の追跡が困難になります。

従来のSRAM削減アプローチの限界

型幅削減や定数のフラッシュ配置などの静的最適化は有効ですが、入力データが変動するストリーミング処理では一時領域が残ります。リングバッファもピークを下げにくく、圧縮は計算量と遅延を増やします。さらに動的確保は断片化を生み、長時間稼働で最悪ケースが表面化します。一方でバッファサイズを小さくし過ぎると、取りこぼし対策として再送制御などが必要になり、結果的にコードサイズと検証工数が増大します。

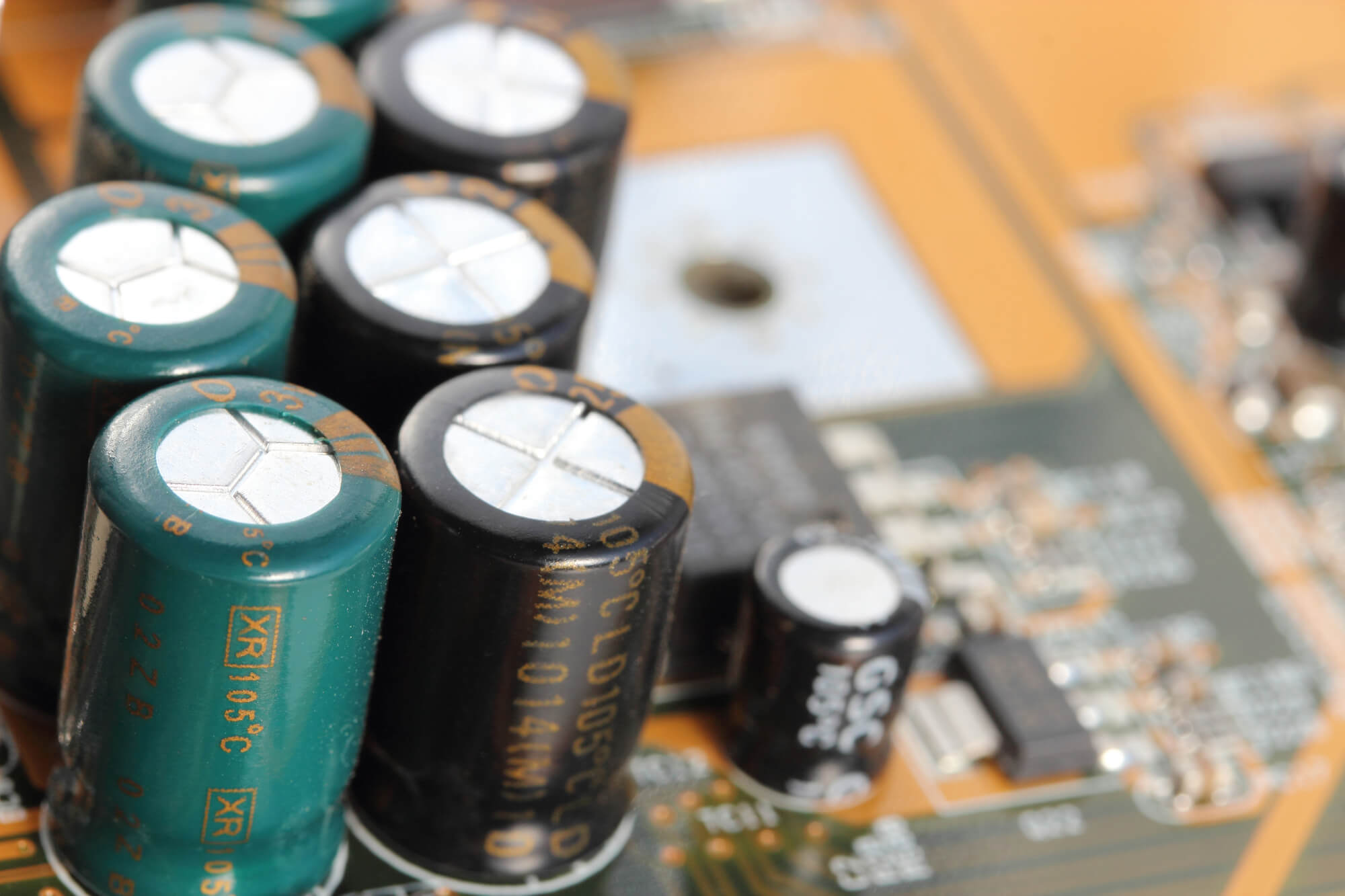

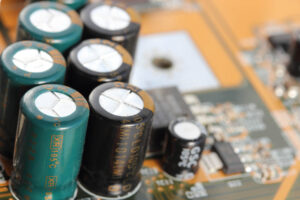

FRAM直接書き込み技術の基礎

FRAMは不揮発でありながらSRAMに近い書き込み速度を持ち、事前消去なしで上書きできます。この特性により一時退避を経ずに直接保存する構成が可能です。FRAMを単なる外部記憶ではなく、実行時のデータ空間として扱うことでバッファの削減を実現します。

FRAMの書き込み特性とSRAMとの違い

FRAMは強誘電体の分極反転を利用するため、フラッシュのようなブロック消去が不要で、バイト単位のランダム書き込みが可能です。書き換え耐性も高く、頻繁な更新に向きます。一方でSRAMは揮発性で待機電力が必要ですが、レイテンシは最小です。FRAMは若干の書き込み電流増加や周辺回路制約があるものの、データ保持と高速性を両立します。特にログ用途では、受信直後に永続化できるため二重バッファを省けます。消去待ちがないことで遅延のばらつきが小さく、リアルタイム制御にも適しています。

FRAMをメモリ空間として扱う設計手法

内蔵FRAM搭載MCUでは、リンカスクリプトでデータセクションをFRAMに配置し、ポインタ経由で直接更新できます。外付けFRAMでも、ドライバ層で抽象化すれば配列のように扱えます。重要なのはキャッシュやバッファを介さず、アプリ層から即時書き込みする経路を設けることです。書き込み完了のタイミングを明確にし、電源断に備えたフェイルセーフ手順を組み込みます。メモリマップト方式ではアクセス権限や保護機構も設計に含め、誤書き込みを防止します。

直接書き込みにおける信頼性と耐久性

FRAMは高い書き換え回数を持ちますが、無制限ではないため更新頻度の分散設計が必要です。ログ構造化やウェアレベリング的配置で局所的集中を避けます。さらに、電源断時の途中更新に備え、ヘッダとデータの確定(コミット)フラグによるアトミック更新やチェックサムを導入します。エラー検出符号を併用すれば、バスノイズや瞬断による破損も検出可能です。

SRAMバッファ削減を実現するデータ構造最適化

SRAM削減を本質的に進めるには、単なる容量圧縮ではなくデータの流れを再設計し、FRAMへ直接保存する前提で中間バッファや多段コピーを排除します。

コピー型設計からゼロコピー設計への転換

従来は受信後にSRAMへ格納し、整形してから永続領域へ書く二段構えが一般的でした。これを受信直後にFRAMへ記録する経路へ変更すれば、中間バッファを不要化できます。ポインタを直接永続領域へ向け、処理もその場で行うことでコピー回数を削減します。さらにDMA転送先をFRAMに設定すれば、CPU介在を減らせます。整合性を保つ最小単位を定義し、途中状態を残さない更新順序を設計します。ゼロコピー化は速度向上だけでなく、SRAMピーク使用量の抑制に直結します。

永続データ構造の設計ポイント

FRAMを主記憶として扱う場合、電源断後もデータの不整合を起こさない構造が求められます。固定長レコードやログ構造を採用し、更新は追記型にすることで破損影響を局所化します。ヘッダに世代番号や有効フラグを持たせ、アトミックに切り替える手法が有効です。また、可変長データはインデックステーブルで管理し、断片化を抑制します。これによりSRAM上の一時整形領域を持たずに直接更新を可能にします。

性能・消費電力・面積のトレードオフ評価

SRAM削減は面積と待機電力の低減に寄与しますが、FRAMアクセス頻度が増えると書き込み電流やバス占有が課題になります。実測でレイテンシと電流波形を確認し、周期タスクへの影響を定量化します。バッファ廃止で減るコピー時間と、直接書き込みで増える待ち時間を比較し、必要に応じてキャッシュライン単位のバッファを最小限残すなど、システム全体のエネルギーと応答時間から最適点を判断します。

SRAM削減を成功させるためのFRAM設計アプローチ

FRAMを活用したSRAM削減を安全に行うためには、対象バッファの選定から評価、検証までの体系的な移行アプローチが必要です。

削減対象バッファの特定と優先順位付け

最初に全バッファのサイズ、最大使用量、更新頻度を洗い出し、ピークSRAM消費への寄与度を定量化します。ログ、通信、キャッシュなど用途別に分類し、書き込み後すぐに保存するデータなど、永続化と親和性の高い領域から移行を検討します。リアルタイム制約や障害時の影響度を評価し、段階的な削減計画を立てます。数値に基づく優先順位付けにより、検証範囲を限定しつつSRAM使用量を確実に削減できます。

FRAM適用可否の技術判断基準

FRAM適用の可否は、アクセス頻度、書き込みサイズ、許容レイテンシで判断します。高頻度更新でも耐久性は十分ですが、バス帯域が逼迫する場合は分散書き込みを検討します。電源断時の整合性要件が厳しい場合はA/B面のダブルバッファリング等を前提に設計し、読み出し中心のデータはSRAM残置も選択肢とします。温度範囲や保持年数などの環境条件も照合し、安易な全面置換によるリスクを回避します。

実装時の設計チェックポイント

実装ではリンカ設定、ドライバ遅延、割込みとの排他制御を確認します。書き込み中に割込みが入る場合はクリティカル区間を明確化し、データ破損を防ぎます。さらにエラー検出符号やバックアップ領域を設け、異常時の復旧手順を実装します。評価では長時間連続書き込み試験と電源瞬断試験を実施し、最悪条件での挙動を確認します。設計レビューではメモリマップと更新順序を重点的に確認し、SRAM削減と信頼性維持の両立を図ります。

RAMXEEDが提供するFeRAM製品一覧

https://www.ramxeed.com/jp/products/feram-products