データ保持電源電圧とLDO設計:不安定な残電圧下で信頼性を保つ方法

SRAMのデータ保持電圧とLDO設計の課題を解説します。低電圧環境でのエラー要因や、機器の信頼性を守る対策を整理しました。また、解決策として不揮発性メモリを活用する選択肢も紹介します。

目次

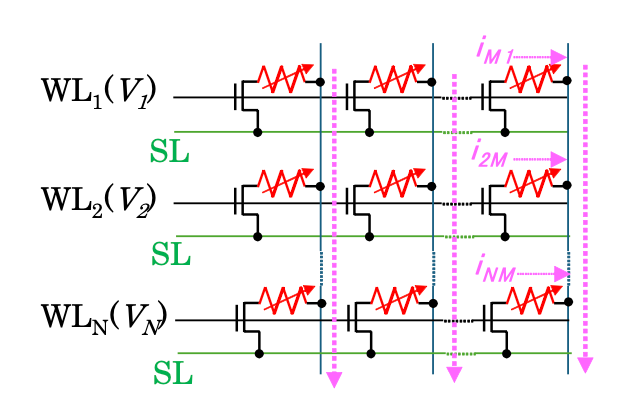

SRAMのデータ保持電源電圧(VDR)とLDO設計の関係

SRAMのデータ保持電源電圧は、揮発性メモリが電源供給中にデータを安全に保持するために必要な最低電圧条件を示す重要な設計指標です。LDOはこの電圧を安定的に供給する役割を担い、特に電源変動時において保持電圧を下回らない制御が求められます。両者は密接に関連し、電源設計全体の信頼性を左右します。

データ保持電圧とは何かと設計上の重要性

データ保持電圧(VDR)とは、メモリセルが書き込まれた情報を失わずに維持できる最低限の電源電圧を指します。この値はプロセスばらつきや温度条件、リーク電流の影響を受けるため、設計時には十分なマージンを確保する必要があります。特にSRAMでは、保持電圧を下回ると即座にデータ破壊が発生し、システムの信頼性に直結します。そのため、バックアップモードを持つ電源系設計ではこの電圧を基準にした保護設計が不可欠です。

SRAMにおける電圧マージンの考え方

SRAMの設計においては、理想的な保持電圧だけでなく、最悪条件を想定した電圧マージンの確保が不可欠です。プロセスばらつきや温度変動、電源ノイズなどにより実際の動作電圧は変動するため、単純な仕様値ではなく統計的な分布を考慮する必要があります。さらに、LDOの出力誤差や急激な負荷変動による瞬間的な電圧ディップも加味することで、実環境における安全動作領域を定義することが重要です。

電源低下時に発生する保持エラーのメカニズム

電源電圧が低下すると、メモリセル内のフリップフロップの維持能力が低下し、論理状態の識別が不安定になります。この状態ではノイズやリーク電流の影響を受けやすくなり、ビット反転やデータ消失が発生します。特に電源が緩やかに低下する場合、LDOがドロップアウト領域に入り出力が追従できなくなることで、保持電圧を下回る時間が長くなります。このような過渡的な電圧不安定領域が、実際のフィールドでのデータ破壊の主因となります。

LDO設計における低電圧・残電圧動作の課題

LDOは入力電圧が十分に確保されている状態では安定した出力を維持できますが、残電圧環境ではその性能が大きく制約されます。特に入力電圧の低下に伴いドロップアウト領域に入ると、出力制御性が低下し、保持電圧の維持が困難になります。こうした条件下での挙動理解が信頼性設計の鍵となります。

ドロップアウト電圧とヘッドルームの制約

LDOにおけるドロップアウト電圧は、入力電圧と出力電圧の最小差分を規定する重要なパラメータであり、残電圧環境ではこの制約が直接的に影響します。入力電圧が低下しヘッドルームが不足すると、パス素子は完全にオン状態となり、制御ループが機能しなくなります。この結果、出力電圧は入力電圧に追従するだけの状態となり、安定した電圧供給ができなくなります。さらに周囲温度の上昇によりドロップアウト特性が悪化することもあり、設計時には最悪条件を想定した余裕設計が不可欠です。

入力電圧低下時の出力不安定要因

入力電圧が低下する過程では、LDO内部の制御ループが徐々に動作限界に近づき、出力電圧の安定性が損なわれます。特にループゲインの低下や位相余裕の減少により、出力にリップルや振動が発生しやすくなります。また負荷変動が重なると、出力電圧のディップが増幅され、瞬間的に保持電圧を下回るリスクが高まります。さらに入力電源自体にノイズや揺らぎがある場合、それがそのまま出力に伝播しやすくなるため、システム全体の信頼性に影響を与えます。

誤差アンプ・リファレンスの低電圧動作限界

LDOの精度を支える誤差アンプやバンドギャップリファレンスは、一定以上の電圧での動作を前提として設計されています。そのため入力電圧が低下すると、これらの回路が正常に動作できなくなり、出力電圧の制御精度が急激に悪化します。特に基準電圧(リファレンス)が不安定になると、出力電圧そのものが設計値から逸脱し、保持電圧を下回る危険性が高まります。また低電圧時にはオフセットやノイズの影響も相対的に大きくなるため、設計段階で動作限界を把握し、適切な安全マージンを確保することが重要です。

不安定な残電圧下でのデータ保持・信頼性確保手法

残電圧が不安定な環境では、LDO単体の性能だけでなく電源システム全体としての対策が求められます。特に電源ディップや瞬断などの過渡的な変動に対し、保持電圧を下回らない設計が重要です。複数の設計手法を組み合わせることで、実環境におけるデータ保持信頼性を確保することが可能になります。

電源ディップ・瞬断時の動作保証設計

電源ディップや瞬断が発生した場合でもデータ保持を維持するためには、電圧降下(放電)の速度を制御する設計が重要です。具体的には、入力側および出力側に十分な容量を持つキャパシタを配置し、時定数を稼ぐことで保持電圧を下回るまでの時間を引き延ばします。また、LDOの過渡応答特性を考慮し、急峻な負荷変動に対しても安定した出力を維持できる構成とすることが必要です。さらに、電源監視回路と連携し、危険な電圧領域に入る前にマイコンをスリープさせる設計も有効です。

PSRR・過渡応答を活用した電圧安定化

PSRRは入力電源のノイズやリップルが出力にどの程度影響するかを示す重要な指標であり、残電圧環境ではその重要性がさらに高まります。高いPSRR特性を持つLDOを選定することで、入力電圧の揺らぎを抑え、出力電圧の安定性を確保できます。また過渡応答性能が優れているLDOは、急激な負荷変動に対しても電圧ディップを抑制できるため、保持電圧を維持する上で有効です。これらの特性を総合的に評価し、用途に適したデバイスを選択することが重要です。

デカップリングと電源シーケンス設計

デカップリングコンデンサの適切な配置は、電源ラインのインピーダンスを低減し、瞬間的な電圧変動を吸収する上で不可欠です。特にメモリの電源ピン直近に配置することで、ローカルな電圧安定性を向上させることができます。また電源シーケンス設計により、各ブロックへの電圧供給タイミングを制御することで、不安定な状態での誤動作を防ぐことが可能です。これらの手法を組み合わせることで、残電圧環境においてもシステム全体の信頼性を高い水準で維持できます。

不揮発性メモリ利用の可能性とFRAMという選択肢

データ保持信頼性を抜本的に向上させるには、LDOによる電圧維持だけでなく、メモリデバイスそのものの選定を見直すアプローチも有効です。特に微細化による低電圧化が進む中、従来のSRAM+バックアップ電源という構成は設計の限界に近づいています。

SRAM+LDOによるデータ保持設計の限界

SRAMを用いた保持設計では、バックアップ電池の寿命管理や大容量コンデンサの実装面積、そしてLDOの極めてシビアな電圧制御が常に課題となります。特に数マイクロアンペアの待機電流を年単位で維持する設計は、部品点数の増加とコストアップを招きます。また、電源電圧のわずかなノイズでデータが消失するリスクを完全に排除することは難しく、よりシンプルで堅牢なデータ保持手法への要求が高まっています。

保持電圧(VDR)を不要にする不揮発性メモリの特徴

不揮発性メモリは、電源供給が完全に遮断された(0Vになった)状態でもデータを保持できるため、SRAMで苦労していた保持電圧(VDR)の管理自体が不要になります。これにより、LDOによる高度な残電圧制御やバックアップ用回路を大幅に簡略化、あるいは削除することが可能になります。電源断の瞬間にデータを保護するという設計思想から、電源がなくても消えないという物理的特性を活用することで、システムの消費電力低減と信頼性向上の両立が期待できます。

SRAM同等の書き換え耐性を持つ「FRAM」の可能性

不揮発性メモリへの移行において最大の壁となるのが「書き換え寿命」ですが、これを解決するのがFRAM(FeRAM、強誘電体メモリ)です。FlashやEEPROMと異なり、FRAMはSRAMと同等の高速書き込みと、10兆回を超える実質無制限の書き換え耐性を備えています。SRAMのような保持用電源を必要とせず、かつ高頻度のログ記録にも耐えうるFRAMは、不安定な電源環境下でのデータ保護における極めて有力な選択肢となります。

RAMXEEDのパラレルインターフェース FeRAMファミリ

https://www.ramxeed.com/jp/product_detail/p-1/

RAMXEEDのQuad SPI対応 FeRAMファミリ

https://www.ramxeed.com/jp/product_detail/s-1/