SRAM容量制約の解消:内部メモリに依存しないFRAMベースのロジック構築

SRAM容量制約に直面する設計エンジニアに向けて、集積密度や消費電力、歩留まりの観点から課題を整理し、内部メモリに依存しないFRAM(FeRAM、強誘電体メモリ)ベース設計への転換方法を解説します。

目次

SRAM容量制約が設計に与える本質的な課題

SRAMは高速ですが、6Tセルの面積効率が低く、増設するとダイ面積とコストが直線的に増えます。さらに低電圧化で安定動作マージンが縮み、容量を欲張るほど設計余裕が減る点が根本課題です。製品要求はログ保持や暗号処理で内部メモリを押し上げますが、SRAM拡大は電源設計、テスト、歩留まりにも波及し、全体最適を難しくします。

SRAMの構造的要因による集積密度の限界

SRAMは一般に6Tセルで構成され、ビット線・ワード線に加えてPMOS/NMOSを6素子配置します。そのため1ビット当たりの面積が大きく、ロジック混載では配線層も圧迫します。結果として容量を増やすほどチップ面積と製造コストが増え、搭載上限を決めます。さらにセル寸法縮小ではばらつき許容が厳しくなり、補助回路や冗長回路を追加しがちです。これらも面積を押し上げ、単純なセル数以上に実効密度を下げます。同一ダイ内でのキャッシュ拡大は有効ですが、ユーザデータ領域までSRAMで抱える設計は、面積効率の観点で早期に限界へ到達します。

大容量化に伴う消費電力とリーク電流の増加

容量を増やすほどビット線容量が増え、読み書きの充放電エネルギーが積み上がります。さらに待機時でもセルのリークと周辺回路のバイアスが支配的になり、スリープ中心の製品では電池寿命に直結します。低電圧化で動作させるほど感度が上がり、読み出し補助やリフレッシュ的な制御を入れると、制御回路分の電力も増えます。結果として、単に「必要だから積む」だけでは、性能・消費電力・熱設計の同時成立が難しくなり、容量制約が実務上の設計制約として顕在化します。

内部SRAM依存アーキテクチャの拡張限界

内部SRAMを前提にすると、タスク間バッファ、ログ、学習用テーブルなどが同一資源を奪い合い、ピーク時に枯渇します。外付けDRAMやフラッシュへ逃がすと、レイテンシ増大と耐久・消費電力の問題が表面化します。結局、内部SRAMを増やすか、機能を削るかの二択になりがちです。さらに量産ではテスト時間、BIST、冗長救済の複雑化が進み、開発リードタイムも延びます。容量不足が単なるリソース問題ではなく、性能保証と製造性まで巻き込む「拡張限界」として現れる点が重要です。

容量制約を生む技術的背景とスケーリングの壁

微細化は論理ゲートに有利でも、SRAMはセル安定性とばらつきに敏感で、電圧を下げるほど読み出し誤りが増えやすい特性があります。大容量化は欠陥確率を押し上げ、冗長やマージン設定が必要になり、面積と設計工数を増やします。組込みでは用途が多様なため、最悪条件に合わせた保守的設計になり、結果として「積めるが使い切れない」状態も起こります。こうした壁を理解した上で、メモリ構成そのものを見直す視点が必要です。

微細化におけるSRAMセル安定性の課題

微細化でトランジスタばらつきが増えると、セルの反転耐性と読み出しマージンが縮みます。特に低電圧動作では、ビット線の微小差分を増幅する感度が上がり、誤判定リスクが増えます。これを抑えるために読み出しアシスト、書込みブースト、ボディバイアスなどを導入すると、回路が増え、検証条件も増大します。結果として、容量を増やすほど「全セルで同じ安定性を保証する」難度が上がり、最終的に動作周波数の引き下げや電圧引き上げで帳尻を合わせることになりやすいです。容量制約はセル数ではなく、保証設計の難しさとして現れます。

高集積化と歩留まりのトレードオフ

メモリアレイは規則的で高密度に見えますが、容量が増えるほど欠陥に当たる確率が上がります。冗長行列で救済できても、冗長分の面積と配線、切替回路、テストパターンが増えます。歩留まりを優先してマージンを広く取ると、動作電圧や速度の目標が遠のきます。逆に性能を優先すると、出荷選別やグレーディングが必要になり、製造コストが上がります。つまり大容量SRAMは「作れるか」より「量産で狙い性能を安定して出せるか」が本質で、設計・製造・テストの三者でトレードオフが固定化します。この構造が容量制約を現実の上限にします。

組込み用途における容量最適化の限界

組込みSoCではキャッシュは局所性で効きますが、ログやチェックポイント、モデル係数のようなデータは容量依存で増え続けます。さらに割込みや無線スタックなど、ピークが同時に来るケースでは、平均使用量ではなく最悪同時使用量で設計せざるを得ません。圧縮やリングバッファで逃げても、結局は破棄ポリシーを決める必要があり、機能安全や品質要件と衝突します。外付けへ逃がすと、起動時間、電力、耐久、セキュリティの課題が増え、設計の自由度が下がります。結果として「内部SRAMを増やして安心」を選びがちですが、それが面積・電力・コストの天井に当たるため、最適化だけでは解けない問題になります。

FRAMベース設計による内部メモリ非依存アーキテクチャ

FRAMは不揮発でありながらランダムアクセスができ、電源断でも状態を保持できます。この性質を活かすと、内部SRAMに寄せていた状態保持やログを、電源管理と一体で再設計できます。つまり容量不足を「バッファを削る」ではなく、「状態を失わない前提で処理を分割する」方向へ転換できます。結果として、ピーク容量に合わせた巨大SRAMを抱えずに、機能と電力を両立しやすくなります。

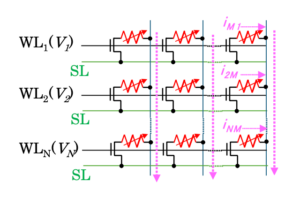

FRAMの基本特性とSRAMとの技術比較

FRAMは強誘電体の分極状態で情報を保持するため、電源断でもデータが残ります。SRAMのように常時給電して状態を維持する必要がなく、待機電力の削減に直結します。またランダムアクセスで書込みが可能なため、フラッシュのようなブロック消去前提の管理が不要になり、ログ更新や小粒度の状態保存に向きます。設計上は「揮発性バッファ」と「永続データ領域」を分ける発想から、「必要な状態を必要な粒度で残す」発想へ寄せられます。速度や容量の最適点は用途依存ですが、ピーク時に溢れる内部SRAMを減らし、電源断復帰やフェイルセーフを簡素化できる点が差別化要因になります。

ロジックと不揮発メモリ統合による設計自由度向上

内部メモリ非依存を狙うには、処理途中の状態をFRAMへ段階保存し、再開可能な実行モデルにします。例えばタスク境界でレジスタ影響を最小化したコンテキスト情報を残せば、深いスリープや瞬断でも復帰が容易です。これにより、SRAMを「常時保持の保険」として積む必要が減ります。さらに暗号鍵や認証カウンタのような保護対象を揮発領域に置かずに済み、キー消失対策と復帰設計を統合できます。重要なのは、メモリ容量を増やすのではなく、状態遷移を設計してデータ寿命を定義することです。FRAMはその実装手段となり、電源管理、エラーハンドリング、ログ設計を一体で最適化できます。

内部SRAM削減による面積・電力最適化効果

FRAMへ状態保存を移すと、ピーク容量に合わせた大容量SRAMを削減でき、ダイ面積を直接圧縮できます。加えて待機時のセル保持電力が減り、スリープ中心のプロファイルで消費電力が下がります。電源断対策としてスーパーキャパシタで長いホールド時間を確保していた場合、必要エネルギーを減らせる可能性もあります。さらにメモリ逼迫による例外処理や退避コピーが減れば、ソフトウェアの実行時間も短縮できます。もちろんFRAM側のアクセス時間や書込み特性を踏まえた配置が必要ですが、「容量が足りないからSRAMを増やす」ループを断ち切り、面積・電力・信頼性を同時に改善する設計余地が生まれます。

SRAM容量制約を踏まえた次世代メモリアーキテクチャ戦略

SRAMの増設は確実な解決に見えて、面積・電力・量産保証の壁に早く当たります。そこで、状態保持の粒度を定義し、不揮発メモリを前提に実行モデルを組み替える戦略が有効です。FRAMを使う場合は、保存対象の選別、アクセス設計、評価指標を明確にし、内部SRAMを「最小限の高速ワーキング」に限定します。こうすることで容量制約を設計の前提条件として扱い、拡張可能な構成へ移行できます。

SRAM依存設計からの脱却ポイント

まず「常時保持が必要な状態」と「再計算できる状態」を分けます。次に、割込み復帰やフェイルセーフで必要な最小状態を定義し、保存粒度をタスク境界やトランザクション境界に合わせます。ログや履歴は寿命と価値を整理し、重要度で層別化して保持期間を決めます。これらを整理すると、内部SRAMを巨大化させる原因が、実は設計上の曖昧さにあることが見えてきます。最後に、SRAMは高頻度アクセスのワーク領域に限定し、永続性が必要な情報は不揮発へ寄せます。この分離ができると、ピーク容量の見積もりが保守的になり過ぎず、面積と電力の両方で設計の自由度が増えます。

FRAM導入時の設計検討事項

FRAM導入では、まずアクセスパターンを可視化し、頻繁に更新される領域と読み出し中心の領域を分けます。次に、バス接続形態(内蔵マクロか外付けか)に応じてレイテンシと帯域を見積もり、キャッシュやバッファの必要量を再評価します。信頼性では、温度・保持特性・書込み耐性の評価条件を仕様へ落とし込み、電源断シーケンスと整合させます。セキュリティ用途なら、アクセス制御と消去手順、暗号化の要否も同時に決めます。最後にソフト側では、チェックポイント位置、整合性フラグ、リカバリ手順を規約化し、評価項目をテストに組み込みます。こうした具体項目を先に固めるほど、FRAMの利点をアーキテクチャとして回収できます。

今後の組込みシステムにおける最適メモリ選定指針

用途別に、求める特性を「速度」「待機電力」「永続性」「更新頻度」「容量」「安全性」で並べ、優先順位を決めます。高速な一時作業が中心ならSRAMを残し、状態保持やログが支配的なら不揮発へ寄せます。電池駆動でスリープが長い製品は、待機電力と復帰時間を指標にし、瞬断耐性が必要ならチェックポイント設計を前提にします。外付けメモリを使う場合は、帯域よりもレイテンシと電力コスト、そして書込み耐久性と書込み管理の複雑さを重く見ます。最終的には、内部SRAMを最小のワーク領域にし、FRAMで状態と履歴を扱う分担が、容量制約に強い構成になりやすいです。

RAMXEEDが提供するFeRAM製品一覧

https://www.ramxeed.com/jp/products/feram-products