電圧スパイクがいかにしてビット反転とメモリ物理破壊を引き起こすか

電圧スパイクがメモリのビット反転や物理破壊を引き起こすメカニズムを解説します。ソフトエラーからラッチアップ等の不可逆な故障へ至る過程や、システムの信頼性を守るための回路設計上の対策を整理しています。

電圧スパイクとは何かと発生メカニズム

電圧スパイクとは、電源ラインや信号線において瞬間的に発生する過渡的な過電圧現象を指します。スイッチング動作や負荷変動、外部ノイズなどが主因となり、ナノ秒からマイクロ秒の短時間で大きな電圧変動を引き起こします。この現象は半導体内部の動作マージンを逸脱させ、一時的な誤動作であるソフトエラー(SEU)や、デバイスの不可逆な物理破壊(EOS)を引き起こす直接的な原因となります。

電圧スパイクの定義と発生要因

電圧スパイクは、理想的な電源供給が維持されている状態から一時的に逸脱し、急峻な電圧上昇や下降、リンギングが発生する現象です。主な発生要因としては、電源スイッチング時の寄生インダクタンス成分による過渡応答、モータやデジタル回路の急激な電流変動、さらには外部からの電磁ノイズや静電気放電などが挙げられます。これらの要因は単独または複合的に作用し、意図しない電圧変動を引き起こし、半導体回路にストレスを与えます。特に高集積化が進む現代のデバイスでは、微小な電圧変動でも動作に影響を及ぼすため、電圧スパイクの理解は不可欠です。

電源ノイズ・グリッチ・EOSの違い

電源ノイズは比較的連続的または周期的に発生する微小な電圧変動を指すのに対し、グリッチは突発的で短時間の異常信号として現れます。一方、EOSはデバイスの耐圧を超える過電圧や過電流によって物理破壊を引き起こす現象です。電圧スパイクはこれらの中間的な位置付けであり、条件次第では単なるソフトエラーに留まる場合もあれば、不可逆な物理破壊に至ることもあります。設計段階ではこれらの違いを明確に理解し、それぞれに応じた対策を講じる必要があります。

半導体内部ノードへの瞬間的影響

電圧スパイクは外部端子だけでなく、トランジスタ間の内部ノードにも瞬時に伝播します。特に微細プロセスでは寄生容量や配線抵抗による遅延の影響により、チップ内部でグラウンドバウンスなどの局所的な電位変動が増幅されやすくなります。この結果、意図しない電荷の移動やしきい値電圧の一時的な変動が発生し、論理状態の不安定化を招きます。こうした内部ノードの電位変動は外部から観測しにくいものの、ビット反転やタイミング異常の直接的な原因となるため、回路設計およびレイアウト設計において十分な配慮が求められます。

電圧スパイクがビット反転を引き起こす仕組み

電圧スパイクはメモリセル内部の電位バランスを一時的に崩し、保持されている論理状態を不安定化させます。特に微細化されたメモリではノイズマージンが縮小しており、わずかな電圧変動でも状態遷移が発生します。その結果、本来保持されるべきビットが反転し、データエラーとして顕在化します。この現象は一過性である場合も多いですが、条件次第では繰り返し発生し信頼性低下を招きます。

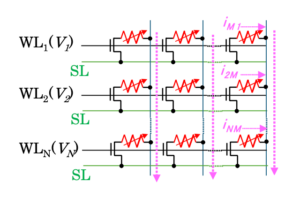

メモリセルの保持原理(SRAM/DRAM)

SRAMはクロスカップルドインバータによって構成され、二つの安定状態のいずれかによりビットを保持します。一方、DRAMはコンデンサに蓄えられた電荷量によって情報を保持しており、定期的なリフレッシュが必要です。これらのメモリはいずれも電圧や電荷のバランスに依存して動作しているため、外乱に対して完全に免疫ではありません。特にSRAMはスタティックノイズマージンが限界に近い条件で設計されることが多く、DRAMは電荷の微小差で状態を判別するため、いずれも電圧スパイクの影響を受けやすい特性を持ちます。

電荷攪乱としきい値超過による反転

電圧スパイクが発生すると、メモリセル内の電荷分布が一時的に乱され、トランジスタのしきい値条件を超える電位変動が生じます。これにより、本来安定していた論理状態が崩れ、反対の状態へと遷移することがあります。特にSRAMでは電源変動によりクロスカップル構造のバランスが崩れることで反転が発生し、DRAMでは蓄積電荷が読み出し判定閾値を下回ることで誤判定が起こります。このような電荷攪乱は短時間であっても影響が大きく、瞬間的なスパイクでもビット反転を引き起こす要因となります。

ソフトエラー(SEU)との関係

ソフトエラーは、物理的な損傷を伴わずにビット反転が発生する現象であり、放射線やノイズなど外部要因によって引き起こされます。電圧スパイクも同様に、デバイスを破壊せずに一時的な状態変化を生じさせるため、ソフトエラーの一種として捉えることができます。特にSEUは宇宙線由来の中性子などが起因として知られていますが、近年では電源品質の悪化やノイズ環境による局所的な電位変動によっても、放射線ヒット時と類似の現象が発生することが確認されています。このため、電圧スパイク対策はソフトエラー低減の観点からも重要な設計課題となります。

ビット反転から物理破壊(EOS)へ至るプロセス

電圧スパイクによる影響は、単なるビット反転に留まらず、条件次第でデバイスの物理破壊へと発展します。初期段階では一過性のエラーとして現れますが、過電圧や過電流が継続または増幅されることで、内部構造に不可逆な損傷が生じます。このように、論理エラーと物理破壊は連続した現象として捉える必要があり、設計段階でその遷移条件を理解することが重要です。

一時的エラーと永久故障の分岐点

ビット反転のような一時的エラーは、電圧条件が正常に戻ることで回復する場合が多いですが、ストレスが一定の閾値を超えると回復不能な状態へと移行します。この分岐点はデバイスの耐圧設計やプロセス特性に依存し、明確な境界が存在しない点が特徴です。繰り返し発生するスパイクによりゲート酸化膜や配線に微細な劣化が蓄積されると、最終的にリーク増加や絶縁破壊が発生し、永久故障へと至ります。そのため、単発のエラーであっても軽視せず、累積的影響を考慮した評価が必要です。

ラッチアップと過電流による破壊

電圧スパイクがトリガとなり、CMOS特有のウェル間に存在する寄生サイリスタ構造が導通するとラッチアップが発生します。この状態では大電流が持続的に流れ、短時間で局所的な発熱が進行します。結果として金属配線の溶断や接合部の破壊が起こり、デバイスは不可逆的に損傷します。ラッチアップは一度発生すると外部からの制御が困難であり、電源遮断などの対処が遅れると致命的な故障につながります。電圧スパイクはこの現象の引き金となるため、設計段階での抑制が極めて重要です。

電圧ストレス蓄積による劣化

電圧スパイクが繰り返し発生すると、瞬間的には問題が顕在化しなくても、長期的にはデバイスの劣化を引き起こします。経時絶縁破壊やホットキャリア注入によるトランジスタ特性の変化が進行し、しきい値電圧のシフトやリーク電流の増加が発生します。このような劣化は徐々に進行するため検出が難しく、ある時点で急激な性能低下や故障として顕在化します。したがって、電圧スパイクは瞬間的な影響だけでなく、信頼性寿命を左右する要因としても重要です。

電圧スパイクに対するメモリ信頼性設計と対策

電圧スパイクによるビット反転や物理破壊を防ぐためには、回路設計およびシステム設計の両面からの対策が不可欠です。電源品質の安定化に加え、メモリ特性を踏まえたデバイス選定や冗長設計を組み合わせることで、エラー発生確率を大幅に低減できます。特に高信頼性が求められる用途では、ノイズ耐性に優れたメモリの採用が重要な設計判断となります。

電圧スパイク対策の設計ポイント

電圧スパイク対策としては、まず電源ラインのインピーダンス低減や、高周波特性に優れたデカップリングコンデンサの適切な配置が基本となります。加えて、グラウンド設計の最適化や電源プレーンの分割制御により、ノイズの伝播を抑制することが重要です。また、サージ吸収素子やフィルタ回路を組み合わせることで、外部からの過渡的な電圧変動を緩和できます。これらの対策は単独ではなく、システム全体として統合的に設計することで効果を最大化できます。

メモリ種別ごとの耐性比較

SRAMやDRAMは高速性や集積度に優れる一方で、電圧マージンが小さくノイズの影響を受けやすい特性があります。特にSRAMは安定状態のバランスに依存しており、微小な電圧変動でも状態が崩れる可能性があります。DRAMも電荷量の差で情報を保持するため、外乱に弱い傾向があります。一方、不揮発性メモリは電子を絶縁膜内に保持する構造的に状態保持の安定性が高く、待機時の電圧スパイクに対する耐性が高い場合があります。ただし、書き込み動作中にスパイクが発生するとデータ破壊を起こすリスクがあるため、用途に応じて適切なメモリを選定することが信頼性確保の鍵となります。

高信頼メモリ(FeRAM)の優位性

FeRAM(FRAM、強誘電体メモリ)は強誘電体膜の分極状態によって情報を保持するため、電荷量に依存する従来メモリと比較して外乱に対する耐性が高い特徴を持ちます。電圧スパイクによる一時的な電位変動が発生しても、分極反転には一定のエネルギーが必要であるため、意図しないビット反転が起こりにくい構造です。また、リフレッシュ不要である点もノイズ影響を受けにくい要因となります。このような特性から、FeRAMは高信頼性が求められる産業機器や車載用途において有力な選択肢となります。

RAMXEEDが提供するFeRAM製品一覧

https://www.ramxeed.com/jp/products/feram-products